# THE IN-SYSTEM CONFIGURATION HANDBOOK: A DESIGNER'S GUIDE TO ISC

Neil G. Jacobson

ANY NON-TEST INSTRUCTION

ISC

ACCESSED

UNPROGRAMMED

00

INSTEUDION

TEST LOGIC RESET

ISQ\_DO'\E-GLEAP

POWER UP

ISC DONE SET

OPERATIONAL

ISC COMPLETE

#### ANY NON-TEST INSTRUCTION

ISC\_DONE SET AND ANY NON-TEST INSTRUCTION LOADED ISC DISABLE

EXECUTED

Digitized by the Internet Archive in 2016

https://archive.org/details/insystemconfigur0000neil

# THE IN-SYSTEM CONFIGURATION HANDBOOK: A Designer's Guide to ISC

# THE IN-SYSTEM CONFIGURATION HANDBOOK: A Designer's Guide to ISC

by

Neil G. Jacobson Xilinx, U.S.A.

### KLUWER ACADEMIC PUBLISHERS Boston / Dordrecht / New York / London

Distributors for North, Central and South America: Kluwer Academic Publishers 101 Philip Drive Assinippi Park Norwell, Massachusetts 02061 USA Telephone (781) 871-6600 Fax (781) 871-6528 E-Mail <kluwer@wkap.com>

Distributors for all other countries: Kluwer Academic Publishers Group Post Office Box 322 3300 AH Dordrecht, THE NETHERLANDS Telephone 31 78 6576 000 Fax 31 78 6576 474 E-Mail <orderdept@wkap.nl>

Electronic Services < http://www.wkap.nl>

### Library of Congress Cataloging-in-Publication

CIP info or:

Title: The In-System Configuration Handbook: A Designer's Guide to ISC Author (s): Neil G. Jacobson ISBN: 1-4020-7655-X

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photo-copying, microfilming, recording, or otherwise, without the prior written permission of the publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Permissions for books published in the USA: <u>permissions@wkap.com</u> Permissions for books published in Europe: permissions@wkap.nl *Printed on acid-free paper*.

Printed in the United States of America

### Dedication

To Dina and Joseph whom I love

### **Table of Contents**

| DE | DI | CA | TI | ON |  |

|----|----|----|----|----|--|

|    |    |    |    |    |  |

PREFACE

ACKNOWLEDGMENTS

XVII

1

1

1

XV

$\mathbf{V}$

**CHAPTER 1: A BRIEF HISTORY OF IN-SYSTEM**

### CONFIGURATION

### 1. BACKGROUND

### 2. PROPRIETARY APPROACHES

2.1.1 LATTICE SEMICONDUCTOR AND IN-SYSTEM PROGRAMMING 3

| viii                          | The In-System Configuration Hand | lbook |

|-------------------------------|----------------------------------|-------|

| 3. STANDARD APPROACH          | ES                               | 5     |

| 3.1 IEEE STD 1149.1           |                                  | 5     |

| <b>CHAPTER 2: CONFIGURABI</b> | LE DEVICE ARCHITECTURES          | 14    |

| 1. INTRODUCTION               |                                  | 14    |

| 2. PROGRAMMABLE LOGI          | C ARCHITECTURES                  | 14    |

| 2.1 SIMPLE & COMPLEX PRO      | OGRAMMABLE LOGIC DEVICES         | 15    |

| 2.1.1 ALTERA CPLD ARCH        | ITECTURES                        | 19    |

|                               | CTOR CPLD ARCHITECTURES          | 20    |

| 2.1.3 XILINX CPLD ARCHIT      |                                  | 22    |

| 2.2 FIELD PROGRAMMABLE        | GATE ARRAYS                      | 23    |

| 2.2.1 XILINX FPGA ARCHIT      | TECTURES                         | 24    |

| 2.2.2 ACTEL FPGA ARCHIT       |                                  | 28    |

| 2.2.3 ALTERA FPGA ARCHI       | TECTURES                         | 30    |

| CHAPTER 3: IN-SYSTEM CO       | NFIGURATION TECHNOLOGIES         | 32    |

### **1. INTRODUCTION**

| 2. ľ | NONVOLATILE | CONFIGURATION | <b>TECHNOLOGIES</b> | 33 |

|------|-------------|---------------|---------------------|----|

|------|-------------|---------------|---------------------|----|

| 2.1   | ANTIFUSE CELLS                                      | 33 |

|-------|-----------------------------------------------------|----|

| 2.2   | <b>ELECTRICALLY ERASABLE AND PROGRAMMABLE CELLS</b> | 35 |

| 2.3   | FLASH ERASABLE AND PROGRAMMABLE CELLS               | 37 |

| 2.4   | <b>VOLATILE CONFIGURATION TECHNOLOGIES</b>          | 39 |

| 2.4.1 | SRAM CELLS                                          | 39 |

| 3. | <b>CONFIGURATION ACCESS PORTS</b> | 41 |

|----|-----------------------------------|----|

|----|-----------------------------------|----|

Table of Contents

| 3.1   | PARALLEL ACCESS                           | 42 |

|-------|-------------------------------------------|----|

| 3.2   | SERIAL ACCESS                             | 45 |

|       | PTER 4: CONFIGURATION DESCRIPTION AND     |    |

|       | CIFICATION LANGUAGES - CONFIGURATION DATA | 48 |

| 1. IN | NTRODUCTION                               | 48 |

| 2. JI | EDEC STANDARD DATA TRANSFER FORMAT        | 49 |

| 2.1   | BASIC FILE ORGANIZATION                   | 50 |

| 2.1.1 | THE L FIELD                               | 50 |

| 2.1.2 | THE C FIELD                               | 51 |

| 2.1.3 | THE V FIELD                               | 51 |

| 2.1.4 | OTHER FIELDS                              | 51 |

| 2.2   | USING JEDEC FILES                         | 51 |

| CILLA | DTED 5. CONFICUD ATION DESCRIPTION AND    |    |

### CHAPTER 5: CONFIGURATION DESCRIPTION AND SPECIFICATION LANGUAGES - CONFIGURATION ALGORITHM WITH DATA SPECIFICATIONS 54

### **1. SERIAL VECTOR FORMAT**

54

| 1.1   | SVF FILE STRUCTURE  | 54 |

|-------|---------------------|----|

| 1.1.1 | THE SIR COMMAND     | 54 |

| 1.1.2 | THE SDR COMMAND     | 55 |

| 1.1.3 | THE RUNTEST COMMAND | 56 |

| 1.1.4 | OTHER COMMANDS      | 57 |

| 1.2   | USING SVF FILES     | 57 |

2. STAPL - STANDARD TEST AND PROGRAMMING LANGUAGE 59

ix

The In-System Configuration Handbook

| 2.1 | <b>BASIC STAPL FILE STRUCTURE</b> | 59 |

|-----|-----------------------------------|----|

| 2.2 | STAPL FILE EXAMPLE                | 61 |

| 2.3 | USING STAPL FILES                 | 63 |

### CHAPTER 6: CONFIGURATION DESCRIPTION AND SPECIFICATION LANGUAGES - SEPARATED CONFIGURATION ALGORITHM AND DATA SPECIFICATIONS 66

### 1. JAVA API FOR BOUNDARY-SCAN 66

| 1.1 JAVA                                            | 66 |

|-----------------------------------------------------|----|

| <b>1.2 WHERE DID JAVA COME FROM?</b>                | 67 |

| <b>1.3 JAVA AND THE WORLD WIDE WEB</b>              | 69 |

| 1.4 JAVA AND IN-SYSTEM CONFIGURATION                | 69 |

| 1.5 DEVELOPMENT OF JAVA API FOR BOUNDARY-SCAN       | 70 |

| 1.6 BASIC JAVA API FOR BOUNDARY-SCAN FILE STRUCTURE | 71 |

| 1.6.1 THE API COMPONENTS                            | 72 |

| 1.6.1.1 The javaScanState Class                     | 72 |

| 1.6.1.2 The javaScanBitIf Interface Class           | 73 |

| 1.6.1.3 The javaScanHWIf Interface Class            | 74 |

| 1.6.1.4 The javaScanOperations Class                | 75 |

| 1.6.2 DATA COMPRESSION                              | 77 |

| 1.6.3 JAVA NATIVE INTERFACE REQUIREMENTS            | 77 |

| 1.7 JAVA API FOR BOUNDARY-SCAN FILE EXAMPLE         | 77 |

| 1.8 USING THE JAVA API FOR BOUNDARY-SCAN            | 97 |

### CHAPTER 7: CONFIGURATION SPECIFICATION AND DESCRIPTION LANGUAGES - IEEE STANDARD 1532

100

### 1. IEEE STD 1532 BSDL

100

| 1.1   | <b>BASIC IEEE STD 1532 BSDL FILE STRUCTURE</b> | 101 |

|-------|------------------------------------------------|-----|

| 1.1.1 | IEEE STD 1149.1 BSDL ATTRIBUTES                | 102 |

| 1.1.2 | THE ISC_PIN_BEHAVIOR ATTRIBUTE                 | 103 |

| 1.1.3 | THE ISC_FIXED_SYSTEM_PINS ATTRIBUTE            | 104 |

| 1.1.4 | THE ISC_STATUS ATTRIBUTE                       | 106 |

| 1.1.5 | THE ISC_BLANK_USERCODE ATTRIBUTE               | 106 |

### Table of Contents

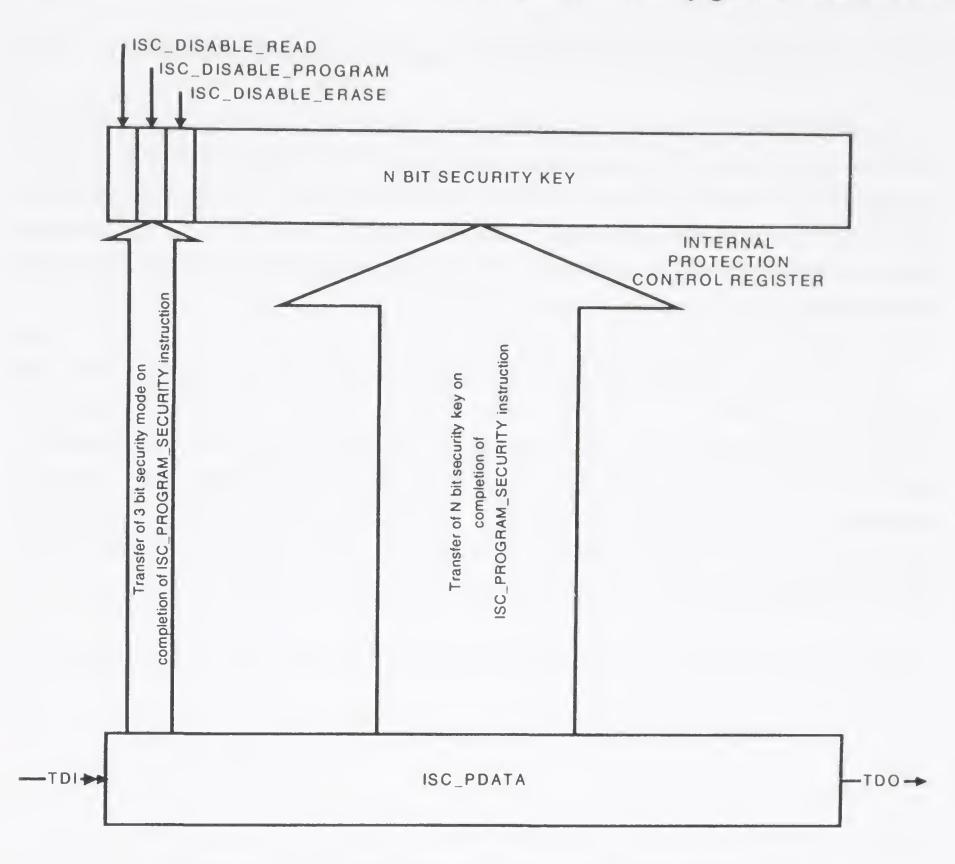

| 1.1 | 1.6 THE ISC_SECURITY ATTRIBUTE                    | 107 |

|-----|---------------------------------------------------|-----|

| 1.1 | .7 DESCRIPTION OF ISC ALGORITHMS IN THE BSDL FILE | 109 |

| 1.1 | I.8 ISC_FLOW                                      | 109 |

| 1.1 | .9 ISC_PROCEDURE                                  | 114 |

| 1.1 | 10 ISC_ACTION                                     | 115 |

| 1.1 | .11 THE ISC_ILLEGAL_EXIT ATTRIBUTE                | 116 |

| 1.1 | .12 THE ISC_DESIGN_WARNING ATTRIBUTE              | 116 |

| 1.2 | IEEE STD 1532 BSDL FILE EXAMPLE                   | 116 |

| 1.3 | USING THE IEEE STD 1532 BSDL FILE                 | 127 |

| 2.  | <b>COMPARATIVE EVALUATION OF APPROACHES</b>       | 133 |

| CH  | IAPTER 8: THE IEEE STD 1532 COMPLIANT DEVICE      | 138 |

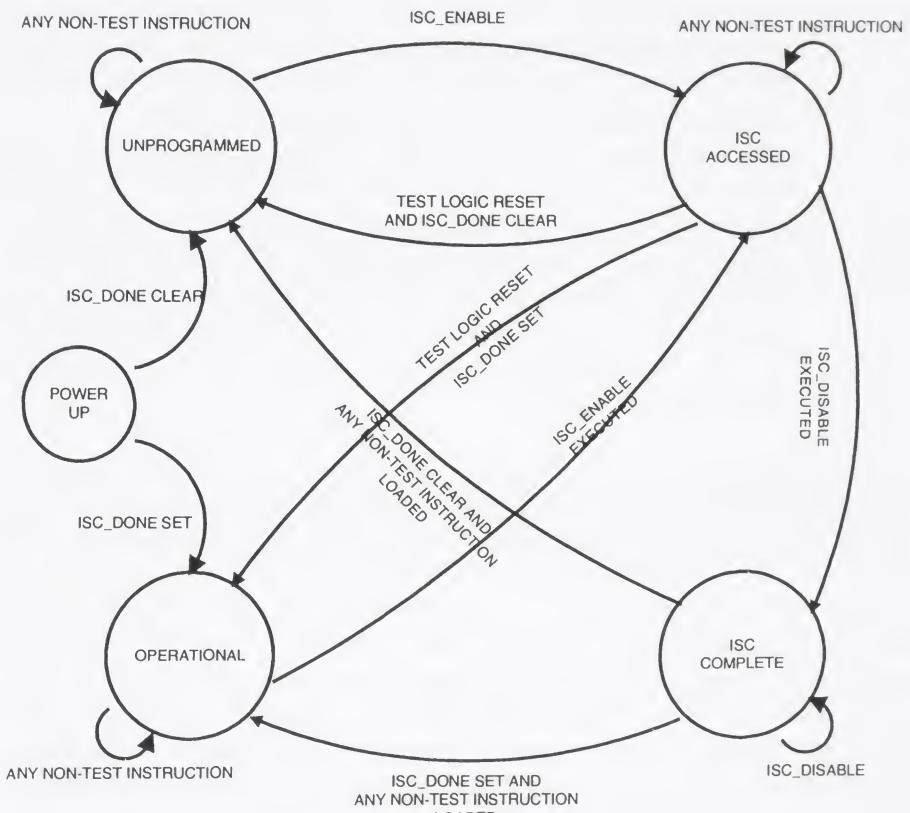

| 1.  | INTRODUCTION                                      | 138 |

| 2.  | OPERATING STATES                                  | 138 |

| 3.  | SYSTEM PINS                                       | 140 |

|     |                                                   |     |

4. ALGORITHMIC OPERATION 141

| 4.1 | ALGORITHM STEPS AND STATE TRANSITIONS            | 141 |

|-----|--------------------------------------------------|-----|

| 4.2 | ALGORITHM OPTIMIZATIONS                          | 142 |

| 4.3 | PROPRIETARY ALGORITHM SUPPORT                    | 144 |

| 4.4 | NULLIFIED INSTRUCTIONS                           | 144 |

| 4.5 | INTERLEAVING TEST AND CONFIGURATION INSTRUCTIONS | 144 |

| 4.6 | ASYNCHRONOUS TRANSITIONS TO TEST LOGIC RESET     | 145 |

| 4.7 | DEVICE OPERATION STATUS INDICATION               | 145 |

| 4.8 | DEVICE OPERATION SUCCESS INDICATION              | 145 |

|     |                                                  | 140 |

## 5. SUMMARY

147

The In-System Configuration Handbook

| CHAPTER 9: DESIGN CONSIDERATIONS FOR IN-SYSTEM<br>CONFIGURABLE SYSTEMS | 148  |

|------------------------------------------------------------------------|------|

| 1. INTRODUCTION                                                        | 148  |

| 2. DEVICE SELECTION CRITERIA                                           | 148  |

| 2.1 IEEE STD 1532 COMPLIANCE                                           | 149  |

| 2.1.1 IEEE STD 1532 COMPLIANT VS. IEEE STD 1532 COMPAT<br>149          | IBLE |

| 2.2 POWER CONSUMPTION DURING CONFIGURATION                             | 150  |

| 2.3 CONFIGURATION SPEED                                                | 151  |

| 2.4 ENDURANCE                                                          | 152  |

| 2.5 DATA RETENTION                                                     | 152  |

| 2.6 SECURITY                                                           | 153  |

| 2.7 RELIABILITY                                                        | 153  |

| 2.8 SYSTEM BOOT TIME                                                   | 153  |

| 2.9 CONFIGURATION PROCESS VALIDATION                                   | 154  |

| 3. SIGNAL LAYOUT CONSIDERATIONS                                        | 155  |

|                                                                        |      |

### 4. SYSTEM POWER CONSIDERATIONS 159

### 5. DEVICE AND SYSTEM TEST CONSIDERATIONS 160

### 6. SYSTEM CONFIGURABILITY CONSIDERATIONS 161

| 6.1   | PROTOTYPING CONFIGURATION            | 161 |

|-------|--------------------------------------|-----|

| 6.2   | PRODUCTION CONFIGURATION             | 162 |

| 6.3   | FIELD UPGRADEABLE                    | 162 |

| 6.3.1 | FIELD UPGRADEABLE – SERVICE ENGINEER | 163 |

| 6.3.2 | FIELD UPGRADEABLE – REMOTE CONTROL   | 163 |

### Table of Contents

| 6.4         | <b>BI-CONFIGURABLE</b>                 | 164 |

|-------------|----------------------------------------|-----|

| 6.5         | FUNCTIONALLY RECONFIGURABLE            | 165 |

| 6.6         | MEDLEY RECONFIGURABLE                  | 166 |

| 7. S        | SUMMARY                                | 166 |

|             | PTER 10: IN-SYSTEM CONFIGURATION-BASED | 168 |

| PLA         | TFORMS                                 | 100 |

| 1. (        | CONFIGURATION ENVIRONMENTS             | 168 |

| 1.1         | PROTOTYPE                              | 168 |

| 1.2         | MANUFACTURING                          | 169 |

| 1.3         | FIELD                                  | 170 |

| 2. I        | PLD MANUFACTURER TOOLS                 | 170 |

| 2.1         | PLD MANUFACTURER SPECIALTY TOOLS       | 171 |

| 2.1.1       | XILINX XSVF                            | 171 |

| 2.1.2       | LATTICE SEMICONDUCTOR ISPVM            | 172 |

| 2.2         | PC-BASED BOUNDARY-SCAN TOOLS           | 173 |

| 3. <i>I</i> | AUTOMATIC BOARD TEST EQUIPMENT TOOLS   | 174 |

- 4. FIELD APPLICATION TOOLS

- 4.1 DIRECT TAP ACCESS METHODS 177

- 4.2 EMBEDDED IN-SYSTEM CONFIGURATION PROCESSOR METHODS 177

176

180

### CHAPTER 11: DESIGNING IN-SYSTEM CONFIGURABLE APPLICATIONS

The In-System Configuration Handbook

| 1.  | THE SPECTRUM OF CONFIGURABILITY          | 180 |

|-----|------------------------------------------|-----|

| 2.  | DESIGNING FOR SIMPLE CONFIGURABILITY     | 181 |

| 3.  | DESIGNING FOR FIELD RECONFIGURABILITY    | 185 |

| 3.1 | DESIGNING FOR NETWORK RECONFIGURABILITY  | 186 |

| 4.  | DESIGNING FOR PERIODIC RECONFIGURABILITY | 188 |

| 5.  | DESIGNING FOR FREQUENT RECONFIGURABILITY | 188 |

| 6.  | DESIGNING FOR RUNTIME RECONFIGURABILITY  | 189 |

| 6.1 | DESIGNING FOR RAPID RECONFIGURABILITY    | 189 |

| 7.  | SUMMARY                                  | 193 |

|     |                                          |     |

**CHAPTER 12: CONCLUSION**

194

### REFERENCES

196

### INDEX

199

### Preface

Programmable logic radically changed the electronic system design landscape. It reduced board space needed for random logic, state machines and system interfaces. It allowed faster design cycles, made easy late term bug fixes and gave designers greater freedom to experiment and prototype.

In-system programming of these devices has had a similar revolutionary effect. The ability to change the programmed content of programmable logic while it is on the board is equivalent to being able to redesign all the hardware - without changing a single component.

This allows the possibility of providing field upgrades of your product to fix problems or to introduce new functionality. It allows designing in reconfiguration as an essential function of your system with different capabilities swapped in as needed during run-time. Further it allows storage of different product profiles for retrieval as necessary to allow just-in-time configuration of systems to meet market needs.

Recent developments in programmable logic have helped in making realizing reconfigurable systems more streamlined. The most significant development, though, was the introduction, approval and popularization of IEEE STD 1532, the IEEE Standard for In-System Configuration of Programmable Devices.

The purpose of this text is to bring together, in a single volume, the information needed by systems designers to develop applications that include configurability. This covers the entire range of systems from the

### The In-System Configuration Handbook

simplest implementations that merely include configurable logic to realize system functions to the most complicated that include reconfigurability as part of the application itself.

While focusing on IEEE STD 1532, the text surveys all the available techniques and products that ease developing in-system configurable applications. In addition, we detail design considerations and rules-of-thumb to ensure the functionality you want will work.

The book begins with a historical perspective on programmable logic. Understanding where you have been often clarifies the present and sheds light in the future. Then we will examine the architecture of programmable logic devices, surveying the most popular devices. From that basis, we will look into the programmable technology at the core of the devices and understand how that works.

After understanding the hardware we are working with, we will survey the infrastructure support provided with these devices. By this, we are referring to the files used to provide programming data for the device. It is here that we gain knowledge of IEEE STD 1532.

From there we study the characteristics of IEEE STD 1532 devices and then begin the analysis of in-system configurable application design. We look into the types of tools available to help you in completing your system and the applicable system design rules. We end with an exploration of the many types of configurable systems and guidelines for their construction.

The object is for this book to be both useful and practical in nature and serve as a reference for developing in-system configurable systems of the

present and the future.

### Acknowledgments

I would like to thank my reviewers C. J. Clark, Dave Bonnett, Vince Eck, Dennis Lia, Mark Moyer, Ken Parker, and Jesse Jenkins. Your exceptional efforts and helpful feedback contributed substantially to this book.

Special thanks to the patient Carl Harris at Kluwer Academic Publishers, who I am certain, never thought he would see this text completed.

I would also like to thank my loving wife, Dina, and my son, Joseph for allowing me to pursue this craziness during what would have otherwise been "our time".

### Chapter 1

### A Brief History of In-System Configuration

### 1. Background

Programmable logic grew from the humble beginnings of Programmable Logic Arrays (PLA) and through Programmed Array Logic (PAL), to Programmable Logic Devices (PLD) and Field Programmable Gate Arrays (FPGA).

Each step in the development increased the speed, flexibility, complexity and capabilities of the devices. As well, the prices decreased. This typical technological evolution led to increasing acceptance and use of the programmable logic.

Worthy of emphasis, though, is that these devices are programmable. They do nothing until programmed with the design personality the end user needs. Early on, the primary purpose of programmability was to get the device working. This wasn't surprising. Programming was complicated and unreliable and typically carried out only once. Soon, the nature of the programmable cell at the heart of these devices allowed for simpler programming techniques. As well, easy reprogramming was possible. Programming then simplified to the point in which the device itself was responsible its own programming. There was no need for external special purpose hardware. This, in turn, led to developing in-system configuration. With in-system configuration, end users could begin to examine the utility of reconfiguration of device contents as an essential part of the system. This is the premise of this book.

### 2. Proprietary Approaches

Some PLDs first incorporated in-system configuration because of the process technology adopted. Manufacturers did not see this as a key selling

point but a means to an end. Later, others developed it as a product differentiator and used it as a key selling point.

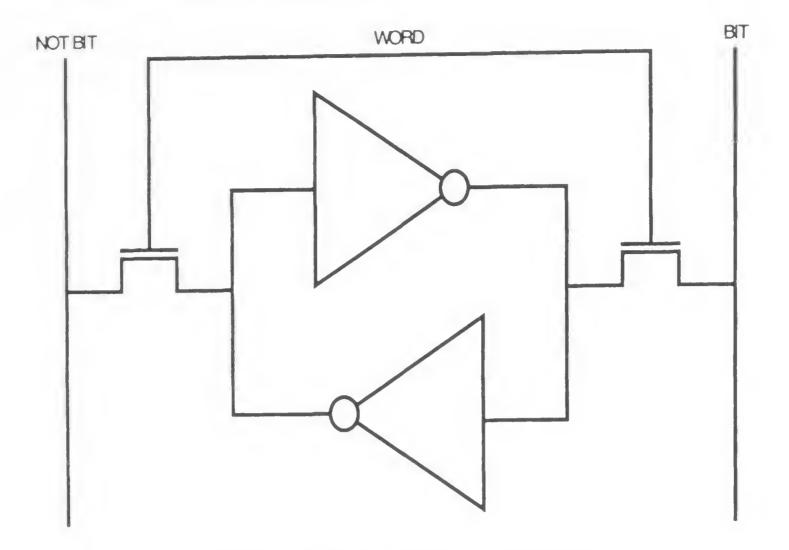

Static read-only memory (SRAM) cell based devices were always insystem configurable. Since the devices had a volatile data store, there needed to be a method to get the configuration bits into the device. Since the technology was new and no applicable standards existed, manufacturers opted for proprietary configuration ports. Typically, manufacturers provided two methods. The first, a serial port, accepted data from a serial programmable read-only memory (SPROM). The second was a parallel port, typically used with a microprocessor or special control logic to load configuration data 8 bits at a time.

Both approaches introduced their own protocols. SPROMs created a new market segment to supply turnkey devices that incorporated the control protocol with a PROM on a single chip. Publishing the protocol allowed end users to fashion their own SPROMs, using some control logic (typically a CPLD) and an off-the-shelf parallel PROM.

An inexpensive, simple microprocessor could use the parallel protocol to do fast and intelligent loading of multiple SRAM devices. This would allow users to manage and optimize the configuration method and configuration store.

The serial protocol was simple and needed fewer device pins. This supported designs with a larger configuration time budget and a greater need for more input and output pins (IO), as well. Using a microprocessor as a configuration controller driving the serial port is also possible.

It wasn't long before users connected the configuration port access and the characteristic reprogrammability of the devices together to incorporate reconfigurability into their designs.

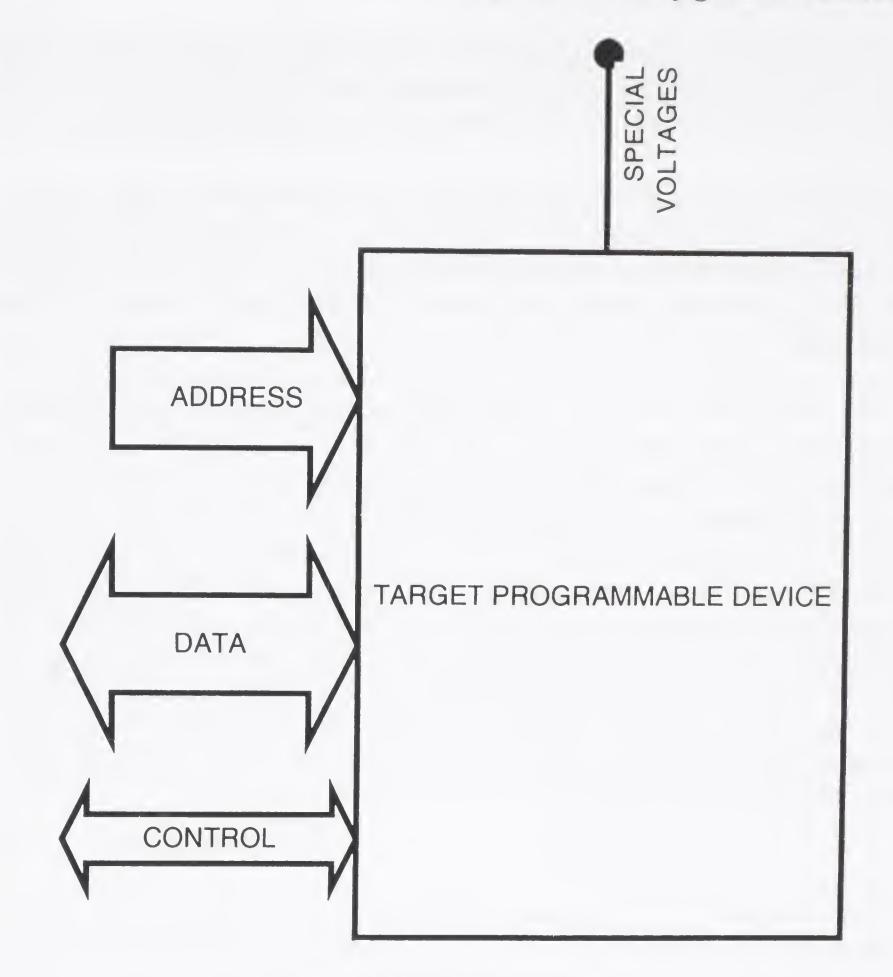

For nonvolatile devices, the path was longer. Early nonvolatile technologies needed special voltages to the device to program the contents. The programming voltages were higher than the typical system voltages of 5 volts. Sometimes, the algorithm needed voltage pulsing with significant pulse-width accuracy to program the device correctly. These special requirements forced the use of special purpose machines known as device programmers to get a device configured. This created a new application for an industry that was already serving the ROM and PROM market. The devices to be configured were inserted in a socket on the device

programmer. An operator would select the programming source file and direct the machine to configure the device with the file's contents. The development of special purpose device handling hardware and special gang programmers increased throughput and fostered integration of this approach into manufacturing flows. Device handlers could pick up a device, insert it in a programmer, retrieve it after configuration, and then place it on the target board for soldering. Gang programmers could program a large group of similar devices with the same data concurrently to increase the programming rate.

Every device had a different algorithm and different voltage needs. Companies that developed device programmers struggled to keep up-to-date with their end user needs.

#### 2.1.1 Lattice Semiconductor and In-System Programming

Process technology advanced and the device geometries shrank. The shrinking feature size allowed for two developments. First, the voltage needed to program nonvolatile cells was reduced. Second, the available die area increased for integration of programming control logic and the generation of on-chip programming voltages. This made the developing insystem configuration possible.

Lattice Semiconductor introduced what they called "In-System Programming" in 1996. A simple four pin serial interface for configuration conserved the number of IO pins needed. The four pins are:

- SDI (serial data input) ۲

- MODE •

- SCLK (serial clock) •

- SDO (serial data output)

These four pins supply programming data to the device and drive an underlying controlling state machine that configures the device.

The SDI pin performs two different roles. First, it acts as the data input to the serial shift register built inside the device. Second, it serves as one of two control pins for the programming state machine. Because of this dual role, the MODE pin controls the role of SDI. When MODE is low, SDI becomes the serial input to the shift register. When MODE is high, SDI becomes a control signal for the programming state machine.

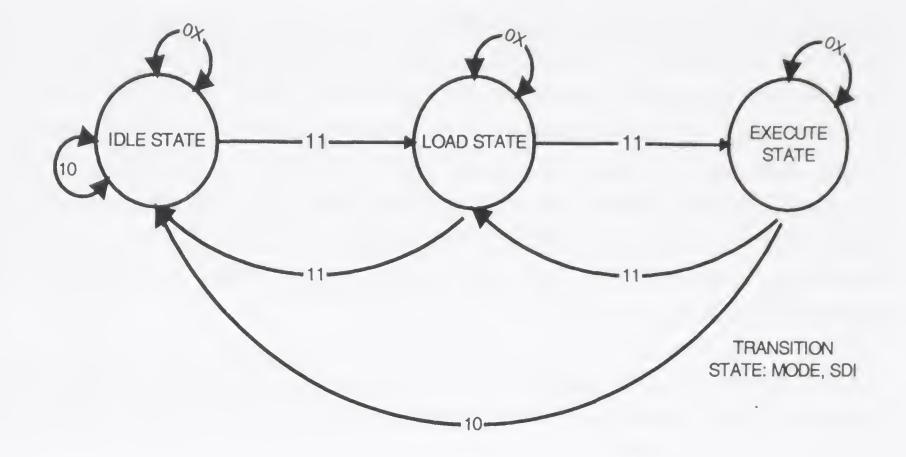

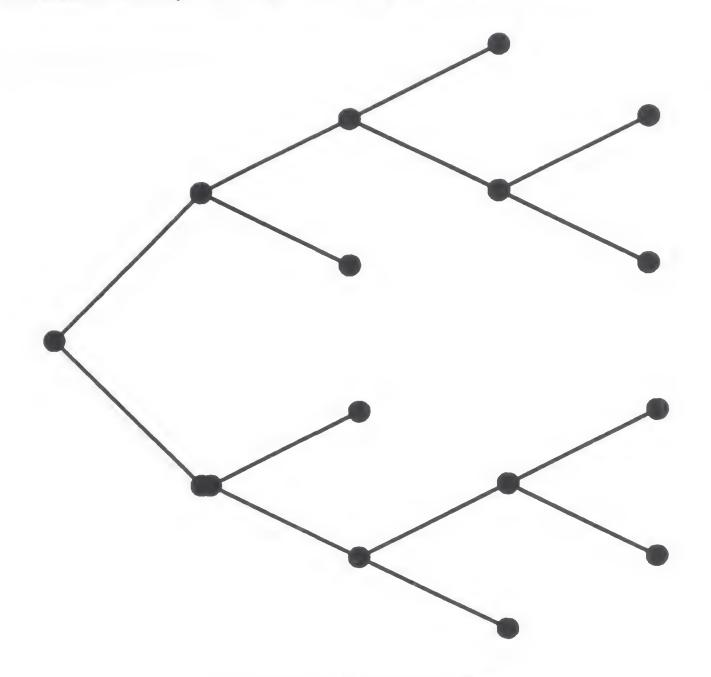

Figure 1-1. Lattice Semiconductor Programming State Machine

This means the MODE signal, combined with the SDI signal, controls the programming state machine.

The SCLK pin provides the serial shift register with a clock. SCLK clocks the internal serial shift registers and clock the programming state machine between states.

The SDO pin connects to the output of the internal serial shift registers. When MODE is high, SDO connects directly to SDI, bypassing the device's shift registers.

The state machine consists of three states: Idle, Load and Execute. The values of SDI and MODE at the rising edge of SCLK control the state transitions. When powered, the device wakes in the idle state. To run a configuration program, the device transitions to the load state to load the instructions and data and then to the execute state to complete the operation.

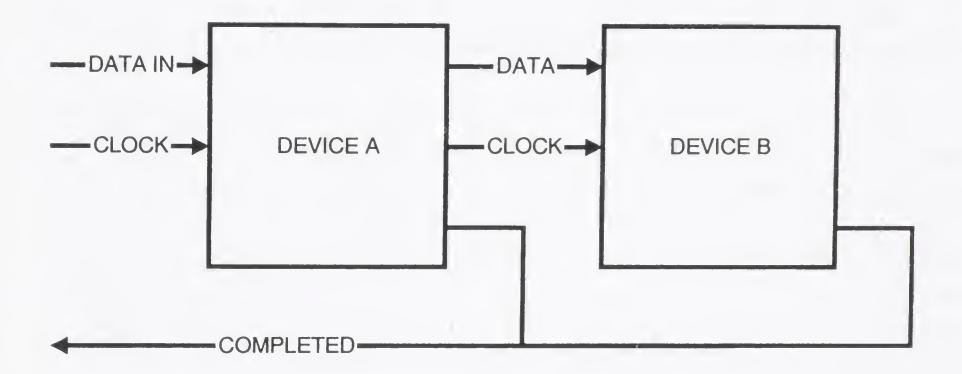

The protocol allowed daisy chaining of Lattice devices and was optimized for use with Lattice Semiconductor's programming algorithms. While this approach provided great utility to users of these specific devices, the protocol was proprietary and Lattice Semiconductor was not keen to share it.

### A Brief History of In-System Configuration

It turned out that was all right since another standard was starting to come into use that was an obvious choice for in-system configuration.

### 3. Standard Approaches

In 1985, a group of European test engineers and technologists gathered to discuss challenges and costs associated with board test. The complexity and price of the automatic test equipment (ATE) because of shrinking packages and falling voltages challenged manufacturers of sophisticated electronics. This group began to discuss ways in which to amend the silicon to include certain testability circuits to offload complexity from the ATE to the device. This group became the Joint European Test Action Group or JETAG.

In 1988, the JETAG engaged engineers from North America in their discussions. This lead to dropping the "E" and thus the Joint Test Action Group or JTAG arrived. This group developed the early proposal for a boundary-scan standard. The standardization was carried out with the backing of the Institute of Electrical and Electronics Engineers (IEEE). In 1990, the IEEE formally approved and published the first boundary-scan standard, known as IEEE STD 1149.1.

### 3.1 IEEE STD 1149.1

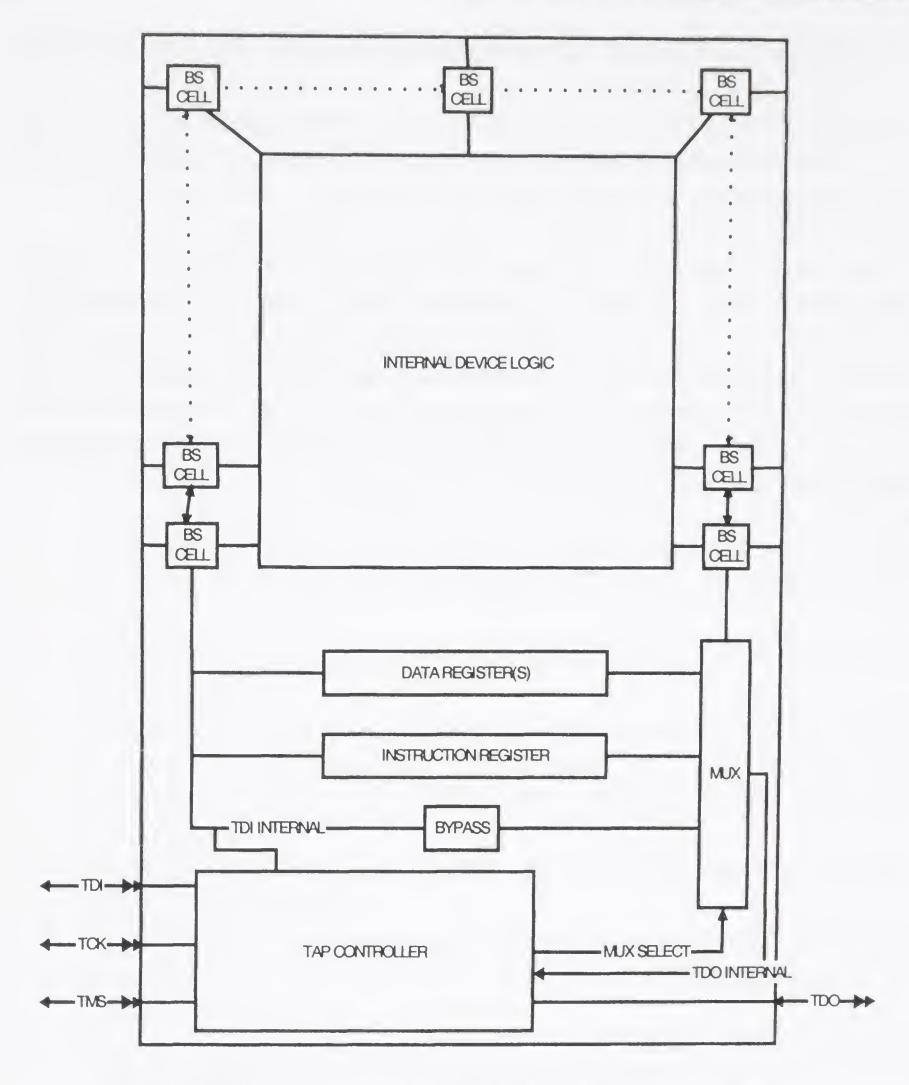

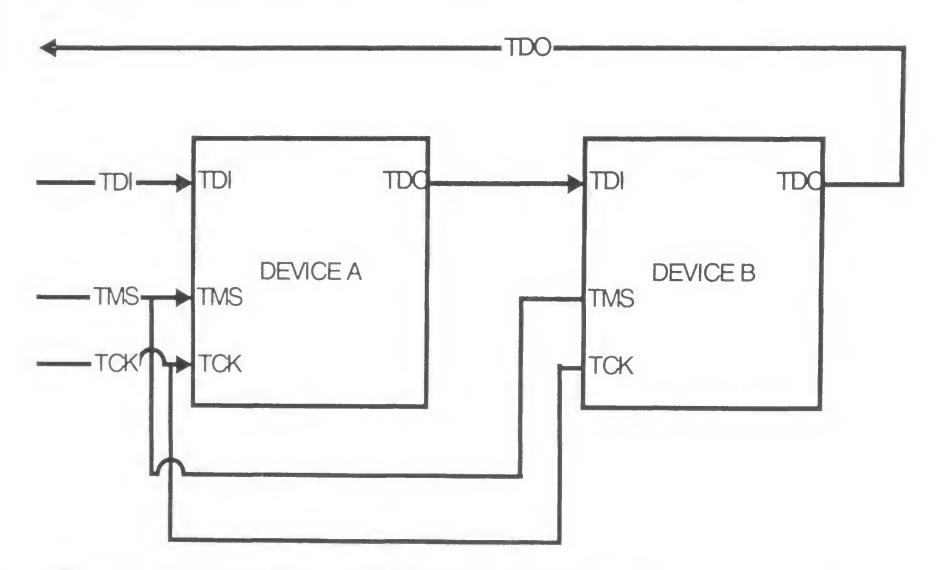

Boundary-scan technology enables engineers to perform extensive debugging and diagnostics on a system through four dedicated test pins. Signals are scanned into and out of the IO cells of a device serially to control its inputs and test the outputs under various conditions.

Devices that support IEEE STD 1149.1 contain a shift-register cell for

each signal pin of the device. These register cells are connected in a dedicated path around the device's boundary. Together these cells are known as the boundary-scan register. This register creates an access path that avoids the normal inputs and provides direct control of the device and detailed visibility at its outputs. Access to and manipulations of this register are controlled by the four test pins and their associated control logic.

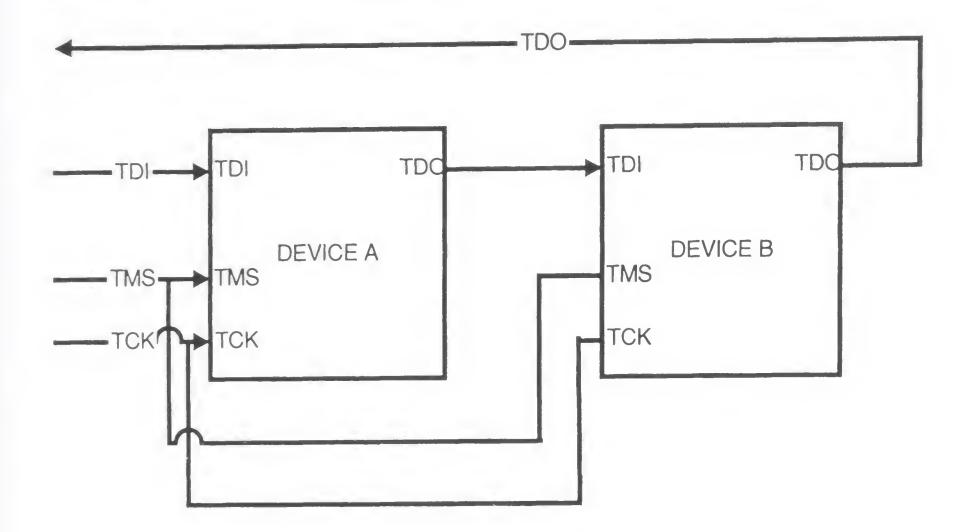

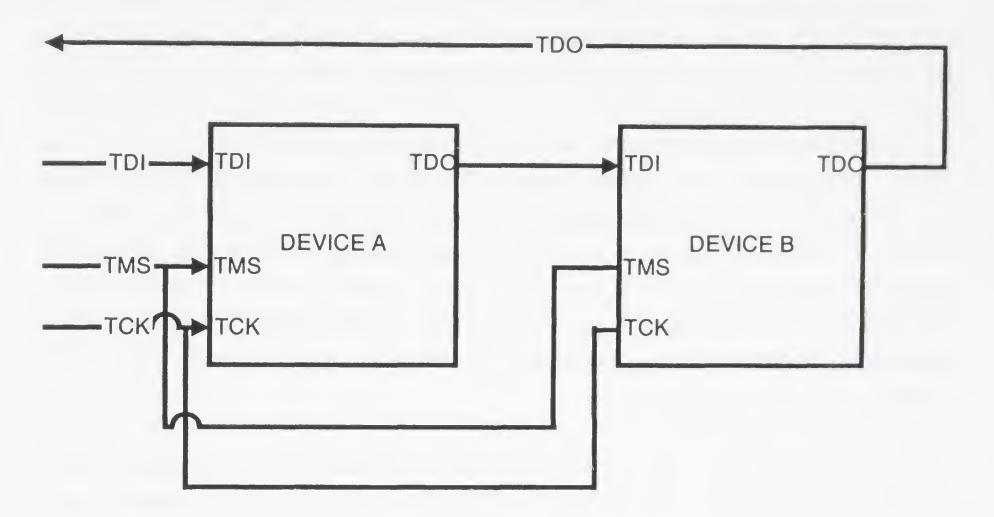

The four boundary-scan control signals, collectively referred to as the Test Access Port (TAP), define a serial protocol port for boundary-scan based devices. The pins are as follows:

• TCK - (Test Clock) - synchronizes the internal state machine operations.

- TMS (Test Mode Select) sampled at the rising edge of TCK to determine the next state.

- TDI (Test Data Input) sampled at the rising edge of TCK and shifted into the device's test logic when the internal state machine is in the correct state.

- TDO (Test Data Output) represents the data shifted out of the device's test logic and is valid on the falling edge of TCK when the internal state machine is in the correct state.

The standard also allows an optional fifth pin called TRST (Test logic Reset). When driven low, this signal asynchronously resets the internal state machine. Because there exists a synchronous method to reset the state machine using the other pins, most IEEE STD 1149.1 devices do not include TRST.

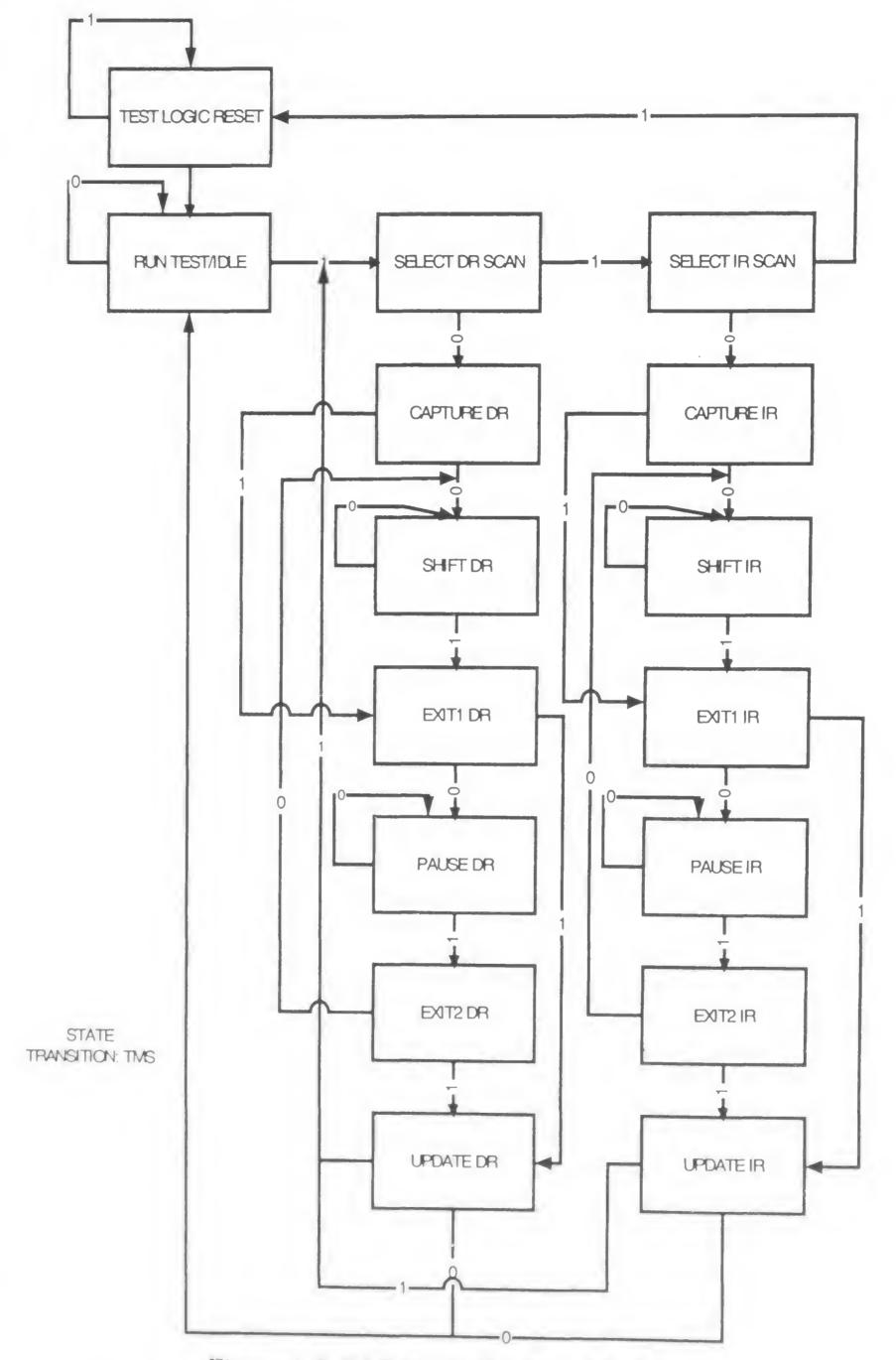

The TCK and TMS (and TRST) input pins drive a 16-state TAP controller state machine. The TAP controller manages the exchange of data and instructions. The controller advances to the next state based on the value of the TMS signal at each rising edge of TCK.

Figure 1-2. TAP Controller State Machine

The sixteen states of the TAP controller state machine are as follows:

- **Test Logic Reset** You arrive at this state by holding TMS high for five TCK pulses. This resets the logic of the TAP controller

- **Run Test/Idle** Operations execute in this state after the associated data has been loaded or simply to wait for signals to settle before sampling them or capturing them.

- Select DR Scan This transitional state leads to either data register operations or instruction register operations.

- **Capture DR** This state loads the selected data register with values typically sampled from the device's pins or from some internal device states. The active instruction defines the behavior.

- Shift DR TDI sampling occurs in this state. In the state, the TAP controller connects a data register between TDI and TDO of length and type determined by the active instruction. With each rising edge of TCK, data shifts into the register from TDI and shifted out on TDO.

- Exit1 DR This transitional state leads to either the Pause DR or Update DR state.

- **Pause DR** This state allows the hardware controlling the TAP a method to break shifts up into smaller bit chunks to ease the processing burden. After completing the pause, the Shift state may be reentered.

- Exit2 DR This is a transitional state that leads either to the Shift DR or Update DR state.

- Update DR The state takes the data loaded in the shift register in the Shift DR state and loads it into he active electronics of the device.

- Select IR Scan This transitional state leads to either instruction

- register operations or the Test Logic Reset state.

- **Capture IR** This state loads the instruction register with values defined by the standard.

- Shift IR TDI sampling occurs during this state. In the state, the TAP controller connects the fixed length instruction register between TDI and TDO. With each rising edge of TCK data shifts into the register from TDI and shifted out on TDO.

- Exit1 IR This transitional state leads to either the Pause IR or Update IR state

- **Pause IR** This state allows the hardware controlling the TAP, a method to break shifts up into smaller bit chunks to ease the processing burden. After completing the pause, the Shift state may be reentered.

- Exit2 IR This is a transitional state that leads either to the Shift IR or Update IR state

- Update IR The state takes the instruction loaded in the shift register in the Shift IR state and loads it to make it become the active instruction.

Each device has only one instruction register. The instruction register length is fixed. Every instruction must have a data register associated with it. The two main paths in the state transition diagram are the DR path and the IR path. The DR path controls the operations on the data registers. The IR path control operations on the instruction register. The data register selected through the DR path is based on the instruction loaded in the instruction register after traversing the IR path.

### Figure 1-3. Block Diagram of an IEEE STD 1149.1 Compliant Device

A transition path like the following loads a new value into the Instruction Register:

- 1. Run Test/Idle

- 2. Select DR Scan

- 3. Select IR Scan

- 4. Capture IR

- 5. Shift IR (shift in instruction bits one at a time)

- 6. Exit1 IR (last instruction bit shifted in)

- 7. Update IR (instruction shifted in now the active instruction)

### A Brief History of In-System Configuration

### 8. Run Test/Idle

Now with an instruction loaded and active, you can load the data needed by the instruction, into its associated data register. A transition path like the following loads a new value into this data register:

- 1. Run Test/Idle

- 2. Select DR Scan

- 3. Capture DR

- 4. Shift DR (shift in data bits one at a time)

- 5. Exit1 DR (last data bit shifted in)

- 6. Update DR (data shifted in now loaded into the device electronics)

- 7. Run Test/Idle

As the new value shifts into the currently selected Data Register on TDI, the captured value shifts out on TDO.

The following data-registers are present in every IEEE STD 1149.1 compliant device:

- The *Bypass* register A 1 bit pass-through register that connects the TDI to the TDO with a 1-clock delay to give access to another device in the daisy chain on the same board.

- The *Boundary Scan* register (BSR) this register intercepts all the signals between the core-logic and the pins and drives the interconnect tests.

IEEE STD 1149.1 defines a compulsory set of instructions that must be present in all compliant implementations. This compulsory set contains the following instructions:

- *BYPASS*: When active, this instruction connects the single bit BYPASS register between TDI and TDO.

- *EXTEST*: When active, this instruction connects the boundary scan register between the TDI and TDO. The device's pin states are sampled and captured by the BSR cells in the Capture DR state. The captured contents of the BSR shift out TDO as new values shift in on TDI in the Shift DR state. The new BSR values are applied to the chip's pins in the Update DR state

The normal sequence used to perform a test operation is:

- 1. Load an instruction that specifies the test performed (say, EXTEST).

- 2. Load the Data Register with values used during this test.

- 3. Optionally, go to Run Test/Idle to wait for applied values to settle.

- 4. Load the Data Register with the next values, while collecting the results of the previous values applied.

- 5. Repeat from step 3 until all values are exhausted.

That represents a quick summary of the features of the boundary-scan standard suitable for interconnect test. This was its primary and intended application.

In 1993, improvements and corrections to the standard were approved. Following that, 1994 saw the approval of a standard language for describing the boundary-scan capacities of an IEEE STD 1149.1 compliant device. This language, known as Boundary-Scan Description Language (BSDL), is input to boundary-scan tools to allow them to understand the manner in which to use a compliant device automatically.

By 1994, the complete boundary-scan infrastructure was available. A well-defined hardware standard was approved and a well-defined boundary-scan capability description language was available. This language was Boundary-Scan Description Language (BSDL). We will learn more about this later. Concurrent with this, device geometries were shrinking and speed and area overhead associated with the test electronics of IEEE STD 1149.1 were acceptable.

This set the stage for the broader adoption of IEEE STD 1149.1 as a device test standard. The true power of the standard, however, was that it defined an extensible architecture. Once the TAP was in place with its associated state machine, there were no limits on defining instructions, data registers, or functions supported.

As the adoption of IEEE STD 1149.1 increased, it made little sense to have a separate proprietary port dedicated to in-system configuration and one for boundary-scan test. Integration of the functionality became certain. This was possible owing to the extensibility of the IEEE STD 1149.1 architecture. Vendors rushed to set up in-system configuration within IEEE STD 1149.1. Each vendor worked alone and developed similar but rather different approaches. Therefore, while the devices could be connected to one another on an IEEE STD 1149.1 daisy chain, there were incompatibilities.

Some devices did not fulfill all of IEEE STD 1149.1, choosing to neglect the boundary-scan test functionality. This left their devices as an interconnect test hole on the board. Other manufacturers used the IEEE STD 1149.1 state machine transitions in an unusual way during programming. This needed special processing for those devices that could harm other devices that had different schemes. Still other devices had unusual or unspecified IO behavior before and during configuration that forced special handling.

The rush to IEEE STD 1149.1 was a hopeful first step. However, it did not reduce the need for customized vendor-specific solutions.

### Chapter 2

### **CONFIGURABLE DEVICE ARCHITECTURES**

### 1. Introduction

Programmable logic is an ideal medium for customized digital designs. Like microprocessors and memories, it offers the well-known advantages of high integration: high complexity and density, small size, low power consumption and cost, and high reliability. Programmable logic also avoids all the problems associated with Application Specific Integrated Circuits (ASIC):

- High Non-Recurring Engineering (NRE) costs (such as those charges associated with mask fabrication)

- Inventory management costs

- Long delays in development and fabrication

- Complex testing issues

- Design issues related to deep sub-micron design rules

This might make programmable logic seem like the only reasonable solution for almost any application. However, some disadvantages have yet to be overcome. For instance, the high cost of high-density programmable devices when compared to similar sized ASICs and the inability of programmable logic to meet the speeds of ASICs. The programmable logic community is rapidly addressing these disadvantages. Before we examine the issues related to the mechanics of configuring programmable devices, let us first get a better understanding of the variety of programmable devices on the market.

### 2. Programmable Logic Architectures

As with most technologies, programmable logic has changed significantly since its first introduction thirty years ago. Understanding this evolution helps shed light on today's situation. In this section, we will provide a survey the architectural evolution of programmable logic devices (PLD) from Simple Programmable Logic Devices (SPLD) to Complex Programmable Logic Devices (CPLD) to Field Programmable Gate Arrays (FPGA).

| Programmable Device Category | Equivalent Gate Range |

|------------------------------|-----------------------|

| SPLD                         | Up to 500             |

| CPLD                         | Up to 50,000          |

| FPGA                         | Up to 5,000,000       |

| ASIC                         | Up to 50,000,000      |

Table 2-1. Gate Capacity for Device Categories

Table 2-1 shows the application space of each evolutionary step. For comparison purposes, Application Specific Integrated Circuits (ASIC) that are semi-custom, mask-programmed devices are included. As programmable logic densities have increased, ASIC densities have as well. But the lower density range of the ASIC market has been quickly won over by PLDs. ASICs have typically been relegated to very high density, very high speed applications. With time, PLDs have been closing the density and speed gap with ASICs.

## 2.1 Simple & Complex Programmable Logic Devices

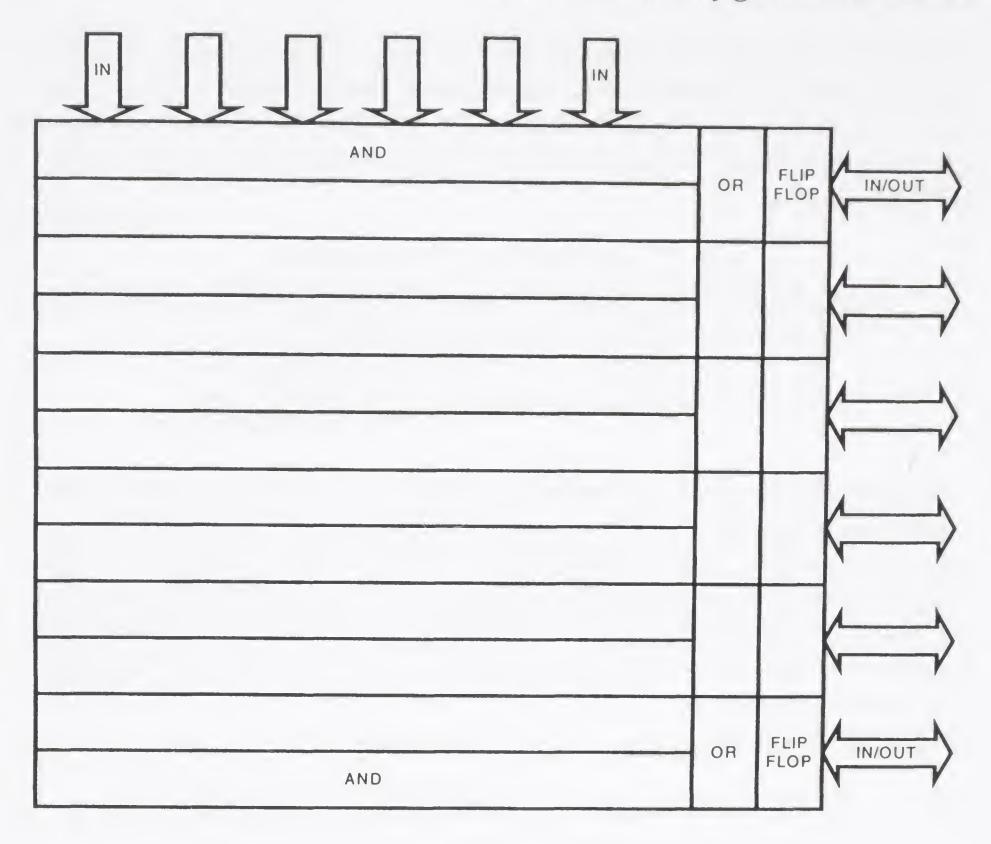

Simple Programmable Logic Devices (SPLD), also known as Programmable Array Logic (PAL), is now an insignificant, rapidly shrinking part of the six billion dollar programmable logic market. It is, however, still of interest to examine their architecture since it laid the groundwork for the architecture of Complex Programmable Logic Devices (CPLD).

Typically, an SPLD consisted of a large switch network that allowed for programmable connections between device inputs and wide input AND gates. As pointed out in Figure 2-1, the inputs went into a product term array that served the purpose of logically ANDing signals together. The outputs of the product term array were then ORed together, creating an AND-OR plane of logic. The output of each large AND gate drove the data input of a flip-flop. Other routing choices were available for each device pin. For instance, some pins could be programmed as outputs and some pin signals could be used a flip-flop clock signals.

The In-System Configuration Handbook

Figure 2-1. Block Diagram of a Typical SPLD

The most popular SPLD device was the 22V10. The name stemmed from the number of available pins on the device (22 being the total number of user available pins on the device, 10 programmable IO and 12 inputs) and the number of registers on the device (10). Many variations on this basic device were made. The general architecture remained the same and the number of IO pins and flip-flops varied.

16

SPLDs like their descendants, CPLDs, featured deterministic and fast pad-to-pad timing. Most SPLDs, however, had only one clock signal available in each device, one output enable and rather limited routing. For these reasons, SPLD's use was limited to implementation of small state machines, address decoders and to consolidate random glue logic.

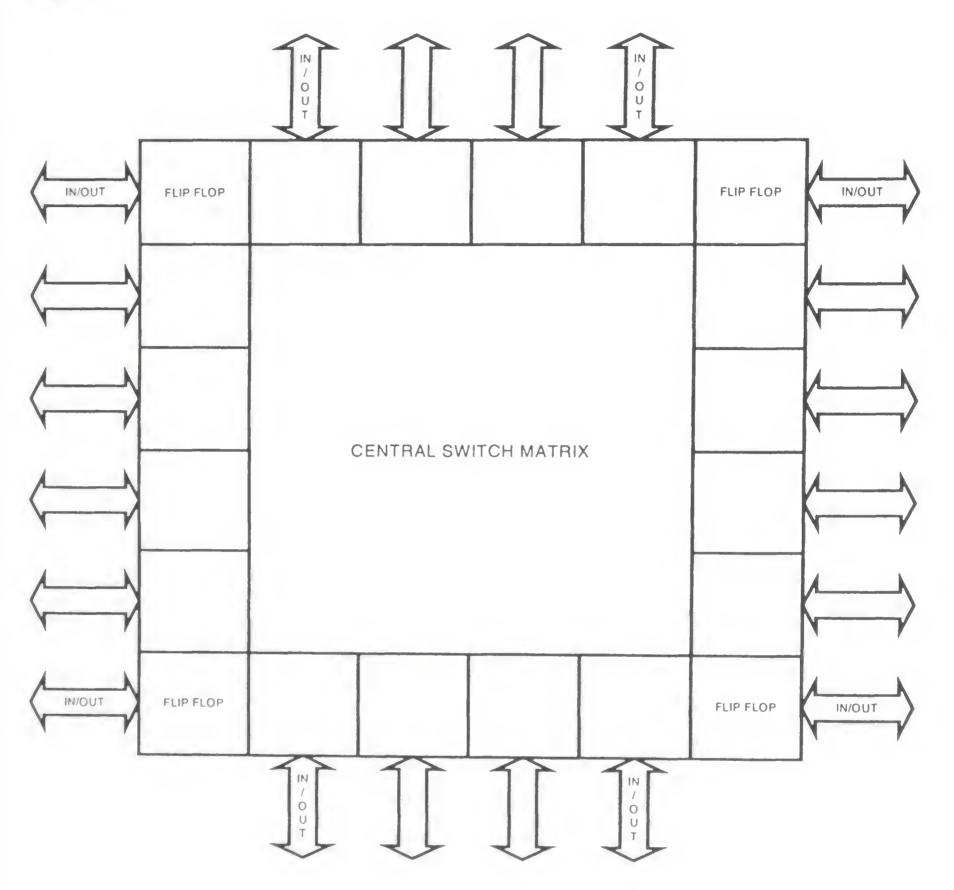

As density and complexity demands increased, the SPLD architecture was no longer applicable. The first variations on this architecture were known as complex programmable logic devices (CPLD). In 2003, CPLDs made up about 35% of the programmable logic market. These devices inherited the AND-OR structure from PALs, but offer more inputs and outputs and better sharing of product terms and more clock inputs.

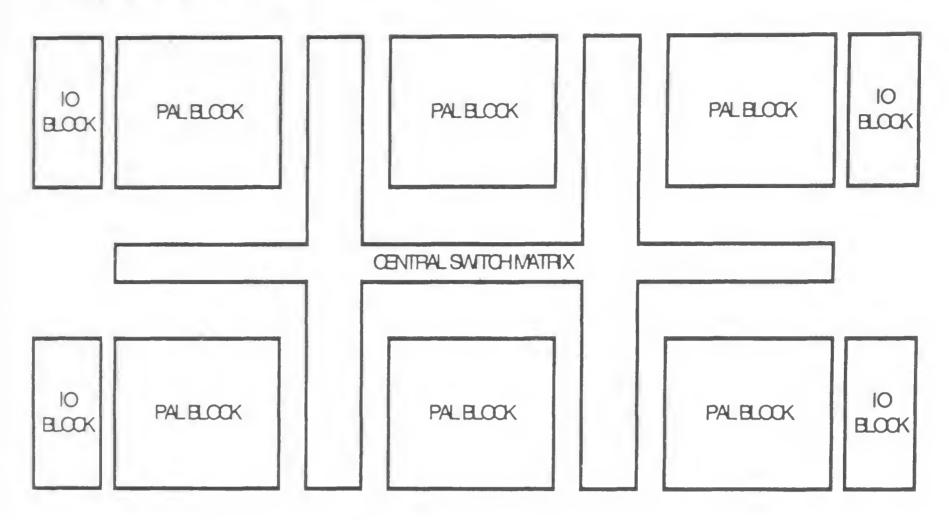

Figure 2-2. Block Diagram of a Typical CPLD

CPLDs have an architecture that results in deterministically calculable speeds with fast pad-to-pad delays. Like the SPLD, there are centralized routing resources. This typically takes the form of either a fully or partially populated central switch matrix (CSM). Looking at Figure 2-2, you will see that in many ways, a CPLD is similar to multiple SPLDs connected by the CSM. Since all signals are routed through the CSM, the CPLD has predictable timing.

The CSM also allows connection of IOs to flip-flops in the CPLD or to other IOs. Typically, each flip-flop has both set and reset inputs whose controlling signal can be flexibly assigned. The implementation logic of the CPLD is typically arranged in macrocells. Each macrocell consists of a wide input programmable logic gate (typically a NAND gate with an invertible output) and a flip-flop with set and reset controls. All paths through the macrocell are programmable and invertible. Each macrocell can therefore be a portion of a random logic function or a portion of a registered state machine.

Typical CPLDs contain anywhere from about 30 to 500 registers. These devices are typically used to realize wide input functions, state machines or data interface logic that is not register intensive. CPLDs are typically nonvolatile devices (meaning that they remember their configuration after power is removed).

The three basic characteristics resulting from the CPLD architecture are as follows:

- High speed

- Nonvolatile configuration

- Deterministic timing

These characteristics represent both the strength and weakness of CPLDs. Their high speed allows them to perform as well as a custom or semi-custom solution. The small board area they consume since they integrate discrete functions and do not need a separate memory to store their configuration helps reduce system cost. Finally, the deterministic timing makes it easy to design them into systems and to predict system performance. Unfortunately, these are strengths that designers view as essential features and thus these device requirements work against increasing CPLD densities using foreseeable process technologies. CPLDs often have high static power consumption, caused by their wired-OR interconnect structure with many sense amplifiers. The Lattice Semiconductor ispMACH 4000 and the Xilinx CoolRunner and CoolRunner2 families of CPLDs offer ultra-low static power consumption.

Since the basic CPLD architecture cannot expand easily to large arrays, CPLDs are inherently limited in size and offer few flip-flops. The limited size (and therefore the limited logical complexity of designable applications) aids in making CPLD design software simple and easy to use, providing rapid design compilation times.

## 2.1.1 Altera CPLD Architectures

The Altera Multiple Array MatriX (MAX) architecture is a typical CPLD architecture. This architecture represents a hierarchical arrangement of erasable Programmable Array Logic blocks using a two-dimensional array structure. It is pictured in Figure 2-3. The design provides multiple level logic, uses a programmable routing structure and is user reprogrammable based on EEPROM technology.

Figure 2-3. Block Diagram of the Altera MAX Device

The MAX 5000 series and the second-generation MAX 7000 series architectures consist of an array of large programmable blocks called Logic Array Blocks (LABs). Each LAB in the MAX 7000 family comprises 16 macrocells. Each macrocell in turn has a programmable-AND/ fixed-OR array and a configurable register. Thus, each macrocell represents a small PLD with five programmable product terms, and it can be configured for either sequential or combinatorial operation. Complex logic functions can be formed using multiple macrocells. In addition, the Altera LAB architecture provides both sharable and parallel expander product terms ("expanders") that can be used to deliver more product terms directly to any macrocell in the same LAB. Finally, at the top level of the design hierarchy, signals are routed between LABs by a Programmable Interconnect Array (PIA). This global routing resource connects any signal source to any destination on the chip.

The MAX 9000 family uses EEPROM nonvolatile programming, and a logic hierarchy built from macrocells that are grouped into LABs as in the MAX 7000 family. However, the routing architecture of the MAX 9000 family uses the FastTrack technology. There are 96 routing channels in each row and 48 routing channels in each column.

## 2.1.2 Lattice Semiconductor CPLD Architectures

The Lattice Semiconductor MACH, pLSI and ispLSI families are variations on the MAX theme.

The MACH family is a collection of PAL-like blocks arranged around a central switch matrix for interconnect. A block diagram of the architecture is supplied in Figure 2-4. The number of PAL blocks is increased to increase the gate density.

Figure 2-4. Lattice Semiconductor MACH Device Block Diagram

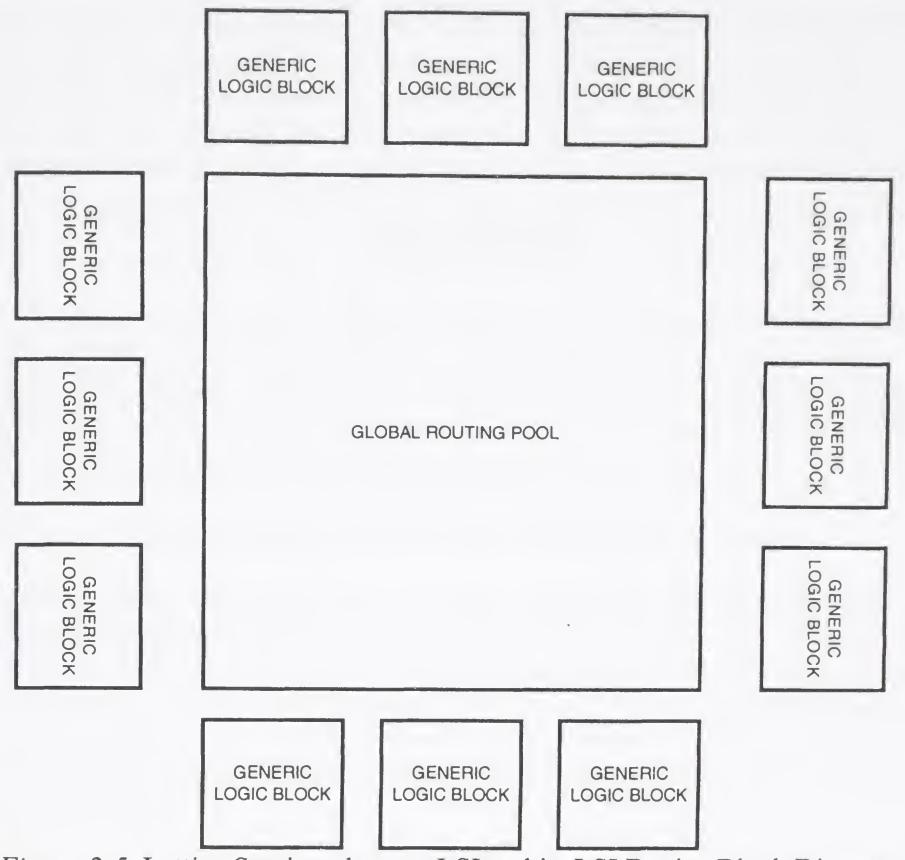

The pLSI and ispLSI devices have a ring of Generic Logic Blocks (basically PALs) around a switch matrix called a Global Routing Pool. As with the MACH devices, all interconnects pass through the GRP yielding predictable timing.

Figure 2-5. Lattice Semiconductor pLSI and ispLSI Device Block Diagram

## 2.1.3 Xilinx CPLD Architectures

The Xilinx 9500 family of CPLDs (including the 9500, 9500XL and 9500XV devices), as well as the Xilinx CoolRunner and CoolRunner2 are all subtle variations on what we have already seen. A collection of logic array blocks or optimized PALs programmatically connectable to one another through a switch matrix.

With the 9500, the switch matrix was unique in that it was a fully populated crossbar switch. This provided guaranteed routability since all paths were possible. For the next generation XC9500XL and XC9500XV devices, the switch was optimized and not fully populated.

The CoolRunner devices use an architecture similar to the Altera MAX but feature an exceptionally low power profile.

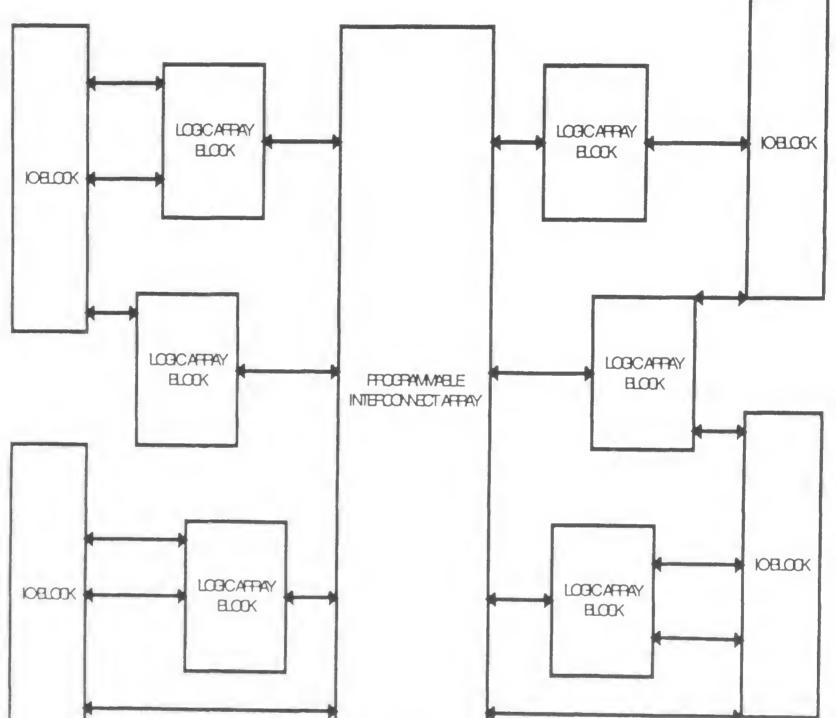

## 2.2 Field Programmable Gate Arrays

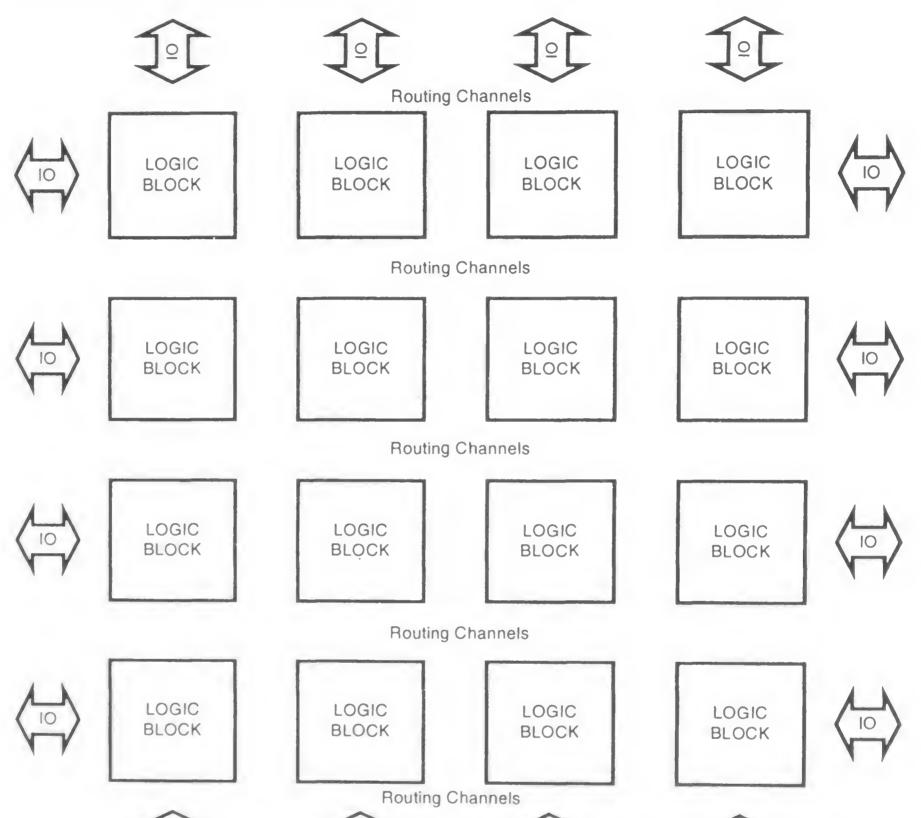

Field programmable gate arrays (FPGA) represent the most popular of the programmable device architectures. FPGAs made up about 55% of the programmable logic market in 2003. They have a more ASIC-like architecture with many flip-flops and distributed routing.

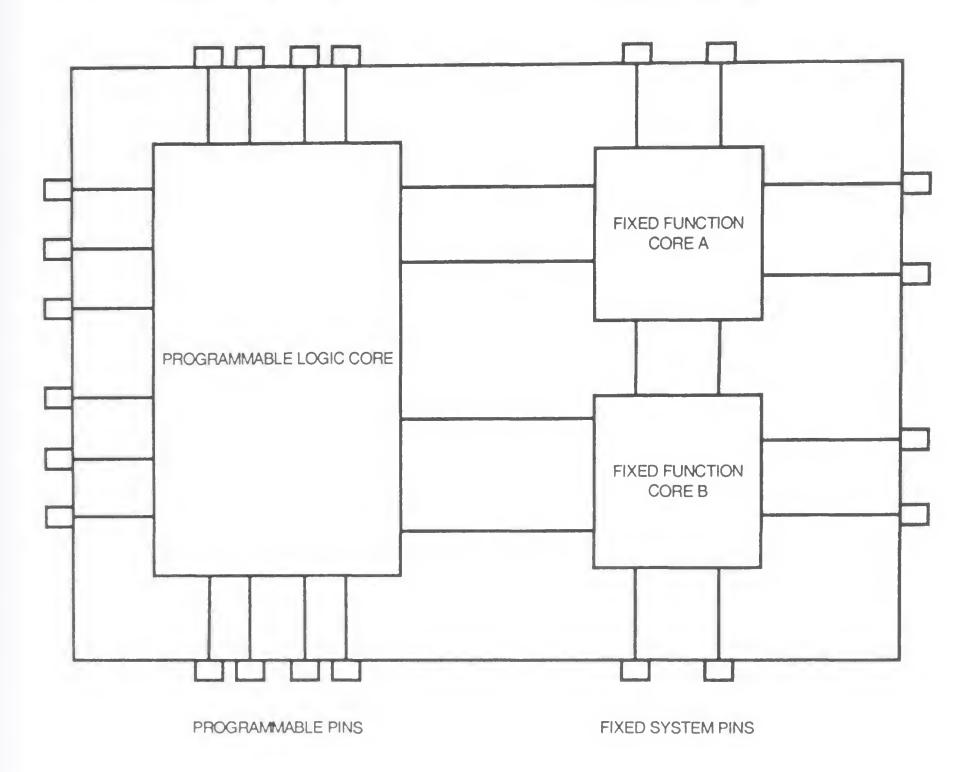

Figure 2-6. Generic FPGA Architecture

The basic FPGA architecture is shown in Figure 2-6. Although there are several varieties of FPGA architectures, they use the same basic approach. The variation is in the number and type of routing resources provided, the functionality of the logic block and the availability of prefabricated cores of specialized functionality. The specialized cores may include microprocessors, high-speed communications transceivers, digital signal processors and other similar complex functions.

## 2.2.1 Xilinx FPGA Architectures

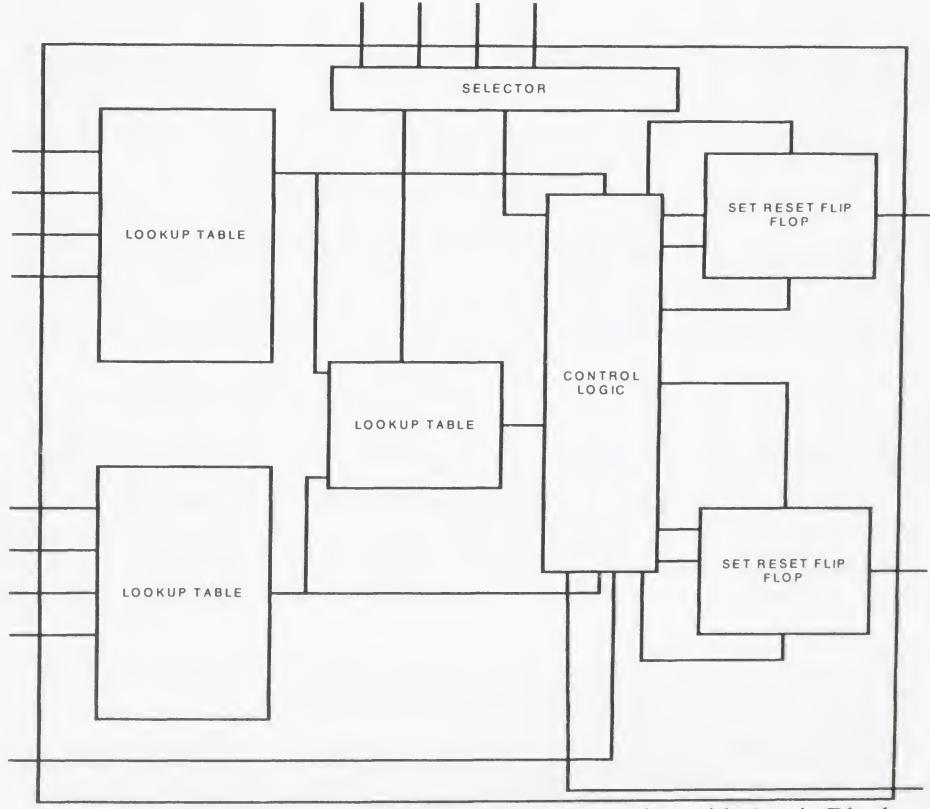

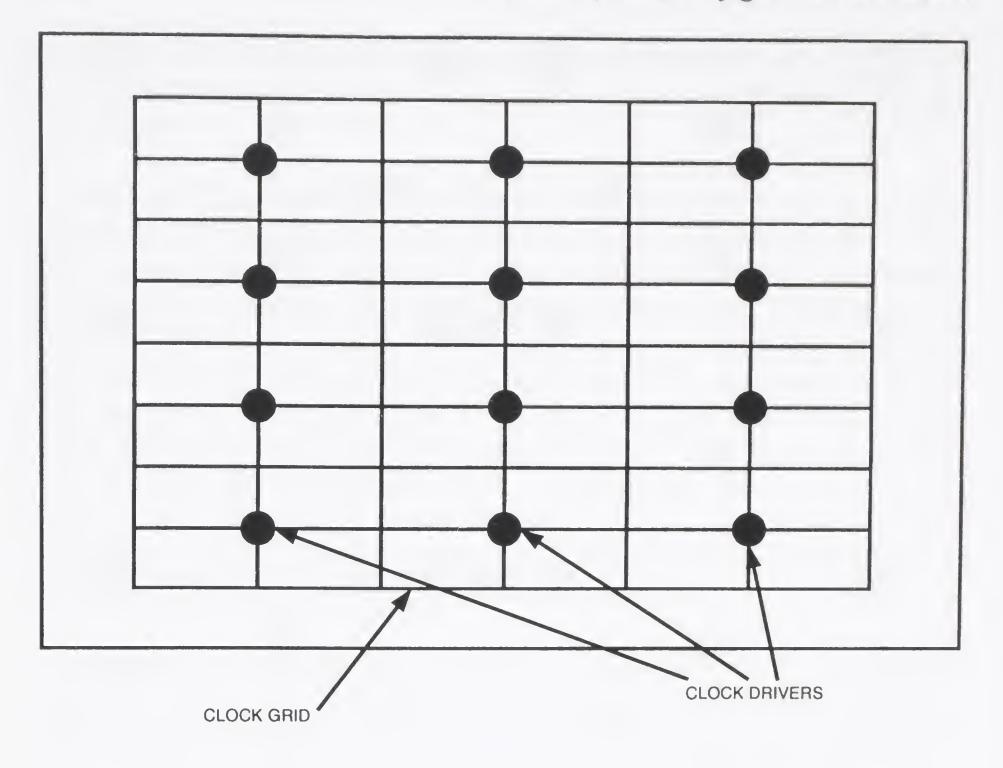

The Xilinx XC4000 family of devices typifies the FPGA architecture. These devices have a routing structure that allows arbitrary point-to-point routing but with limited routing resources. A design is realized by routing signals between configurable logic blocks (CLB). Each CLB consists of two four input look-up tables (LUT) that can act independently or have their outputs routed to one or two constituent latches or flip-flops. Other functions also available are the ability to access the configuration SRAM as a register and the ability to direct the look-up table outputs through another look-up table with an external signal to create functions of up to nine inputs.

Figure 2-7. Block Diagram of Xilinx XC4000 Configurable Logic Block

The Configurable Logic Blocks (CLBs) are organized in a twodimensional array separated by horizontal and vertical wiring channels. Each CLB contains flip-flops, multiplexers, and a combinatorial function block that works as an SRAM based table look-up. Turning on pass transistors customizes connections between CLBs. The pass transistors selectively connect the CLBs to the interconnection resources, or interconnect lines between the horizontal and vertical wiring channels. SRAM cells that are scattered around the chip hold the state of the interconnect switches. Surrounding the CLB array and interconnect channels are the programmable IO blocks which connect to the package pins.

The overall architecture has powerful functional blocks connected to one another by versatile interconnect. This directs design software to pack as much functionality as possible locally in CLBs. In addition, the software tries to limit interconnect dependencies.

The design of the Xilinx CLB and routing architecture is slightly different for each product family. The first generation family (known as the XC2000) is no longer available. It is however interesting to understand its architecture. It contained a CLB with a single D flip-flop and a look-up table that can form any Boolean function of four variables, or two functions of three variables. The routing architecture used three resource types: direct connection, general purpose interconnects, and long lines. Direct connection lines were used to interconnect a CLB with bordering CLBs or IO blocks above, below, or to the right. General purpose interconnects were used for connections which span more than one CLB. There were four horizontal and five vertical general purpose interconnect lines between the array rows and columns, respectively. Each segment ran only the length of a CLB, and then entered a switch matrix that provided programmable connections to adjoining row or column general purpose interconnects. Finally, each horizontal wiring channel had one long line and each vertical wiring channel had two long lines that spans the entire array. These long lines bypassed the switch matrices. They route global signals (for example, clocks), or other signals that needed minimum skew at multiple fan-out points.

The second-generation family was known as the XC3000. In the XC3000 architecture, the logic block (CLB) is expanded and extra routing resources are provided. The CLB can fulfill any Boolean function of five variables or two functions of four variables. Two D-type flip-flops are provided to capture both cell outputs if needed. The routing architecture is similar to the XC2000 family except that each resource type has been improved. Direct connections are allowed to all nearest neighbors and an extra wiring segment is added to the horizontal general purpose interconnect.

As well, an extra long line is added to both the horizontal and vertical channels.

Compared with its predecessors, the XC4000 family adds evolutionary improvements to the basic Xilinx architecture. Greater logic capacity in each CLB is achieved using a two-level look-up table. The 13 input and four output CLB can form any of the following combinatorial logic functions:

- Two independent functions of up to four variables

- Any single function of five variables

- Any function of four variables with some functions of five variables

- Some functions of up to 9 variables

Compared with earlier families, the routing resources of the XC4000 family were significantly increased. The number of globally distributed signals has increased from two to eight, and there are twice as many horizontal and vertical long lines. The number of wiring segments has also more than doubled, and CLB connectivity is improved by allowing most CLB pins to connect to a high percentage of the wiring segments. However, the switch matrix connectivity was reduced to 50% of that of the XC3000 family. The increased efficiency of the associated place and route software indicated that changes in the routing resources were justified. It was demonstrated that FPGA connection blocks needed high flexibility to achieve a high percentage of routing completion, and that relatively low flexibility is needed in the switch blocks.

A significant variation from the XC4000 was the XC5000 device. Architecturally it is still a symmetrical array with SRAM based programmable logic and interconnections. The internal chip organization was dramatically changed. However, the device preserved pin-for-pin compatibility with and had an identical programming and control interface to the XC4000 family.

The logic blocks and their local routing connections were combined into a larger entity called a VersaBlock. The VersaBlocks provided logic and connectivity for efficient assembly of local logic functions. These local functions are then globally interconnected through a General Routing Matrix (GRM). This architecture provides five levels of interconnect hierarchy. This was to be used to exploit the locality of logic in typical digital designs efficiently. Heavily interconnected logic macro-functions placed in bordering CLBs can be locally connected within the VersaBlock. This allows the GRM resources to be devoted to connections between macro-function blocks.

The VersaBlock contains a CLB composed from four separate logic cells (called LC0 through LC3), with a local interconnect matrix. Note that each of the four logic cells within the XC5000 CLB is similar in structure to the original XC2000 family CLB; with a single D flip-flop and a four-variable Boolean function generator. However, grouping four of these independent logic cells in a tightly coupled VersaBlock unit allows efficient high-speed carry chains or high fan-in logic functions to be easily created.

The alternative to this approach is to make interconnect less versatile (and therefore less expensive). With this simplified interconnect, more resources can be dedicated to logic cells by increasing their number.

A device of this sort has a two-dimensional mesh array structure that resembles the gate array "sea of gates" architecture. Like the Xilinx architecture, Static RAM programming technology is used to specify the function performed by each logic cell and to control switching connections between cells. An example of this device is the Xilinx XC6200 family of FPGAs. The design contains 1024 identical logic cells arranged in a 32 X 32 matrix. The design is considered to be a mesh-connected architecture since each cell is directly connected to its nearest north, south, east, and west neighbors. As well as these direct connects, two global interconnect signals are routed to each cell to deliver clock and other "low skew requirement" control signals. The basic array architecture incorporates both nearest neighbor and global connections in the logic cells. Besides these logical connections, row select lines and bit select lines are connected to program each cell's SRAM bits.

The basic building block of the XC6200 design is a configurable cell containing multiplexers and a function unit. Multiplexers that select the source for the X1 and X2 inputs precede the function unit. The function unit can produce any logic function of the two inputs, or of acting as a D-type latch. There are four more multiplexers that select the function output or one of the external inputs for routing to each of the four outputs (north, south, east, and west).

A unique feature in the XC6200 IO pad design is its capacity to provide simultaneous input and output on the same pin when communicating with another device of the same family. This is done through a 2-level (ternary) logic-signaling scheme in which IO pads sense whenever two outputs are driving each other by a contention scheme. Even during contention, the pad can deduce the correct input value and pass it along to the internal circuitry. This makes it easier to partition a single design across multiple FPGAs because the increased connectivity reduces pin limits on communications bandwidth.

The Virtex family of FPGAs (which includes the Virtex and VirtexE devices) represents the fourth generation architecture for Xilinx. It evolved from the XC4000. This architecture represents most devices currently being shipped by Xilinx in 2003. This architecture features more routing resources, a modified CLB and configurable block RAM. A ring of routing resources surrounds the implementation that simplifies interconnections among the LUTs, flip-flops, and GRM. Extra global routing resources are made available and 2 high-speed pass-through routes are included in each CLB.

The most recent addition to the Xilinx family of FPGAs is the Virtex2 family (which includes the Virtex2 and Virtex2Pro devices). Once again, this architecture features further improvements to the CLB and a wider variety of routing resources to promote faster design implementations. In addition, the Virtex2 has more configurable block RAM as well as specific architectural features to simplify clock management and a support wider variety of IO standards.

The Virtex2Pro devices add PowerPC processors and programmable gigabit speed IO transceivers to the fabric of the FPGAs. This allows unprecedented capacity to receive, process and transmit data within the physical boundaries of a single programmable device.

## 2.2.2 Actel FPGA Architectures

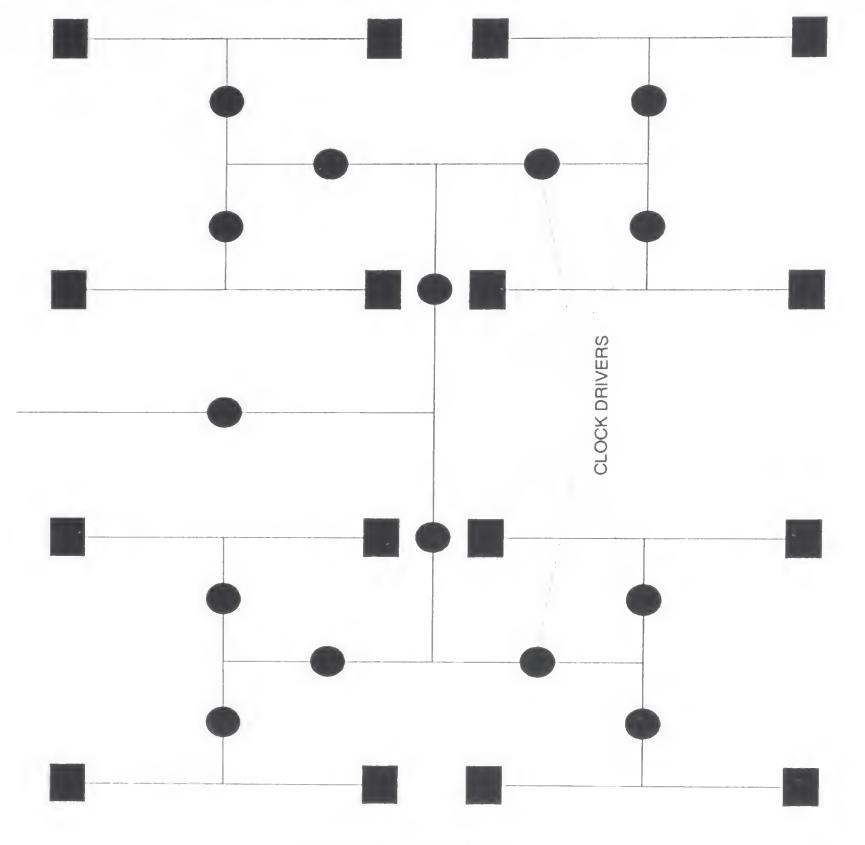

In the Actel ACT<sup>™</sup> family FPGAs, a logic module matrix is arranged as rows of cells separated by horizontal wiring channels. This organization is similar to that found in the traditional style of Mask Programmed Gate Arrays (MPGAs). Vertical interconnect segments of varying lengths are available. Vertical segments in input tracks are permanently connected to logic module inputs, and vertical segments in output tracks are permanently connected to logic module outputs. Long vertical segments are available which are uncommitted and can be assigned during routing. The horizontal wiring channel resources are also segmented into varying lengths. The minimum horizontal segment length is the width of a single logic module,

and the maximum horizontal segment length spans the full channel. Any segment that spans more than one-third of the row length is considered a "long horizontal segment". Connections between interconnect segments are permanently formed using the antifuse. Dedicated routing tracks are used for global clock distribution and for power and ground tie-off connections. Actel has three generations of FPGAs, called ACT1, ACT2, and ACT3.

In contrast to the Xilinx FPGA that uses a complex CLB cell, the Actel approach uses small and simple logic modules. This does not imply that the Actel design has inherent disadvantages compared with the Xilinx approach. Research has shown that both of these approaches have merit.

Research results suggest the best choice for a programmable block depends on the speed performance and the area requirements of the routing architecture. The low-impedance and small area Actel antifuse structure is better suited for use with a simple logic module. On the other hand, the larger area and higher resistance Xilinx SRAM controlled transistor switch is more apt for a complex logic cell.

The ACT1 family Logic Module (LM) is an 8-input, one output function which can be used to build the four primitive logic functions (AND, OR, NAND, NOR) with two through four inputs. The basic ACT1 Logic Module circuit uses multiplexers to create programmable logic functions. The LMs can also be used to make latches, flip-flops, XORs, AND-ORs and other logic structures. Actel does not include dedicated hardwired latches or flipflops in the ACT1 array since they can be built from LMs wherever needed in the design. The ACT1 family uses 22 metal signal wiring tracks in each horizontal channel and 13 vertical tracks that lay on top of each column of LMs.

The ACT2 family is Actel's second generation of FPGAs. It uses two different types of logic modules: a Combinational (C) Module and a Sequential (S) Module. The C module with eight inputs and one output is similar in functionality to the LM used in the ACT1 family. The S-Module is designed to set up high-speed D flip-flops or latches within a single cell efficiently.

An S-module can create an up to 7-input Boolean function followed by a D-type flip-flop or a latch. The S-Module can also be configured with a transparent latch. Then, like the C-Module it can also carry out a purely combinatorial 8-input function. C-Module and S-Modules are paired and then grouped in alternating pairs to form the rows of the ACT2 array. The

ACT2 routing structure is also similar to that of ACT-1, with the same three types of routing resources:

- Vertical input and output segments

- Clock tracks

- Horizontal wiring tracks

However, there are 14 extra tracks in each horizontal wiring channel and two additional tracks in each vertical column.

ACT3 is Actel's third generation FPGA family that uses the same basic array architecture with improved versions of the ACT2 family logic modules. The new C-Module is functionally equivalent to that of ACT2, while the S-Module has been expanded to include a full C-Module driving a flip-flop. The ACT3 architecture contains four clock networks. Two of which are dedicated high-performance clock networks, and two are generalpurpose networks. The ACT3 architecture continues to use the routing resource structure of the ACT2 design with horizontal wiring channels and vertical wiring tracks that overlay the logic modules.

## 2.2.3 Altera FPGA Architectures

The FLEX 8000 series was Altera's first PLD based on SRAM programming technology. This series used a fine-grain hierarchical architecture including 4-input look-up table Logic Elements (LE) as the basic functional building block. LEs are grouped into sets of eight to create LABs as in the earlier family designs. These blocks are arranged into rows and columns. Connections between LEs are provided by horizontal and vertical FastTrack interconnect channels that span the chip. Both the Logic Elements

and the FastTrack interconnects are SRAM programmed in a similar fashion to the Xilinx technology discussed earlier.

The FastTrack interconnect technology is used in the FLEX 8000 part. The LABs are arranged into a two-dimensional array separated by horizontal and vertical FastTrack wiring channels that span the entire array. An advantage of this device wide routing is that it provides predictable wiring delays when compared with segmented FPGA wiring schemes which use a variable number of programmable interconnection points in the routing path. The FLEX 8000 family parts have either 168 or 216 routing channels in each row and 16 routing channels in each column.

### Configurable Device Architectures

Each column of LABs has dedicated lines that route signals out of the LABs and into the FastTrack column. The column interconnects can then drive IO pins or feed into the row interconnects to drive other LABs. The number of wiring channel routing resources varies by family and part type.

Each row of LABs has a dedicated row interconnect for routing macrocell inputs and outputs. The row interconnects can then drive IO pins or feed other LABs on the chip. Each macrocell in the LAB can drive up to three separate column interconnect channels. A row interconnect channel can be fed by the output of a macrocell through a 4-to-1 multiplexer that it shares with three column channels. If the 4-to-1 multiplexer is used for a macrocell-to-row connection, then the three column signals can access another row channel by an extra 2-to-1 multiplexer.

Recent Altera FPGA architectures, like the Stratix and Stratix GX have been subtle variations on the Xilinx Virtex II and Virtex II Pro approaches. Architecturally similar, these devices included different processors than the Virtex II Pro, different block RAM and high-speed transceiver resources.

## Chapter 3

## **IN-SYSTEM CONFIGURATION TECHNOLOGIES**

## 1. Introduction

In the previous section, we looked at the architectures of programmable logic devices in general. Architecture considerations are one of the primary reasons in determining which programmable device a designer will choose. Other considerations are, of course, price, availability, implementation tool performance and, often, corporate guidelines.

However, in designing a reconfigurable system the reconfiguration technology becomes another consideration. In this section, we will examine the variety of configuration technologies used in programmable devices.

The devices discussed so far fall into two broad configuration families: volatile and nonvolatile devices.

Nonvolatile devices keep their configuration information even when the device is powered off. Typically, SPLDs and CPLDs are nonvolatile. This means the boot-up time for these devices is instantaneous. When powered up, a system made with these devices (if they are previously configured) is ready to go.

Volatile devices forget their configuration after power down. This means that these devices need to be reminded of their configuration at power on. This is usually accomplished by keeping the configuration information in a nonvolatile store like a PROM or a disk. The implication is that volatile devices need some finite (and measurable) amount of time after power on to be reloaded with their configuration before being ready to go. FPGA devices typically are volatile.

| Feature           | Antifus<br>e | SRAM       | EEPROM             | FLASH               |

|-------------------|--------------|------------|--------------------|---------------------|

| Nonvolatile       | Yes          | No         | Yes                | Yes                 |

| Reconfigurability | No           | Yes        | Yes                | Yes                 |

| Endurance         | 1 cycle      | Infinite   | < 10,000<br>cycles | ~ 100,000<br>cycles |

| Programming time  | Minutes      | < 1 second | < 10 seconds       | < 2 minutes         |

| External Prom     | No           | Yes        | No                 | No                  |

| Power-up time     | Instant      | < 1 second | Instant            | Instant             |

Table 3-1. Configuration Technology Characteristics

A small subgroup of FPGAs uses antifuses to control their interconnect structure. Thus, these devices preserve their configuration when powered down, they power-on instantly, and they need no external configuration memory. This non-volatility comes at the cost of reconfigurability. Antifuse-based FPGAs are usually one-time-programmable. In addition, device programming often takes several minutes. These antifuse-based devices represent about 6% of the FPGA market.

## 2. Nonvolatile Configuration Technologies

We will examine three separate configuration technologies in this section:

1. Antifuse cells

2. Electrically erasable and programmable cells

3. Flash erasable and programmable cells

## 2.1 Antifuse Cells

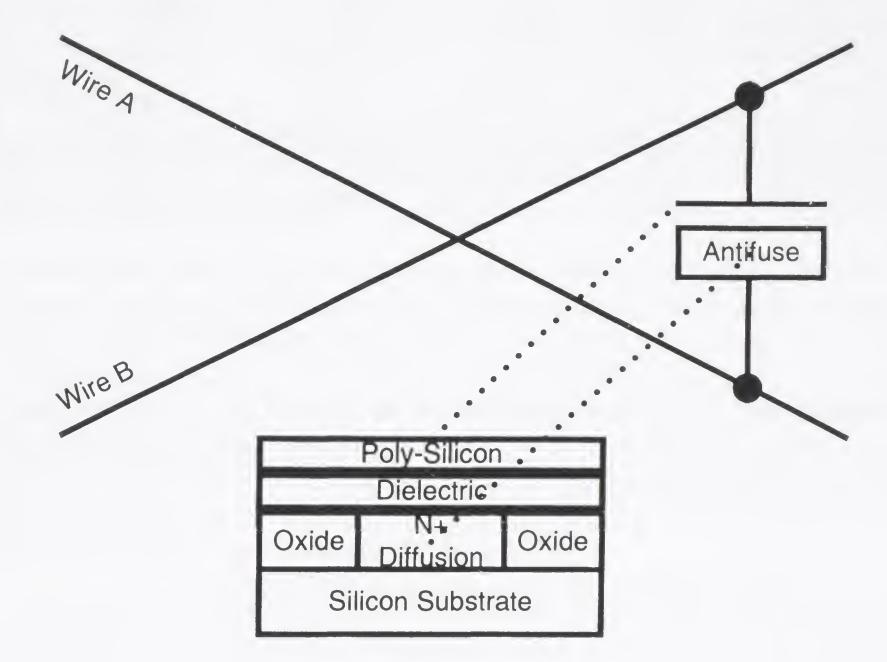

Actel, QuickLogic and others have introduced commercial products that use antifuse programming. In Actel FPGAs, a Programmable Low-Impedance Circuit Element (PLICE) antifuse element is used. The normally high antifuse resistance (>100 Megaohms) is permanently changed to a low resistance (200-500 ohms) by applying suitable programming voltages. The programmed antifuse is used to make a direct electrical connection between two metal lines. Adding three specialized masks to a standard CMOS process is needed to make the PLICE antifuse. The physical structure illustrated in Figure 3-1, consists of an Oxide-Nitride-Oxide dielectric layer sandwiched between a top polysilicon layer and a bottom N+ diffusion layer. Applying a high voltage (about 18V) across the device and driving a high current through the link dielectric completes the programming. This causes the dielectric to melt and results in a conductive link between the top and bottom terminals.

Figure 3-1. The Anti-Fuse Element

QuickLogic also adds a unique three-layer structure to the standard CMOS process to create their antifuse element, that they call a ViaLink. The ViaLink uses an amorphous silicon layer that is sandwiched between the first and second metal layers. An unprogrammed ViaLink has greater than 1 Mohms resistance and, like the PLICE antifuse, is programmed by applying a higher than normal voltage. The resulting high current through the amorphous layer causes it to permanently change to a conductive state with a typical resistance of only 80 ohms. The area occupied by these antifuse elements is small when compared to the other programming alternatives. While this contributes to improved on-chip gate density, the large area needed for the high-voltage transistors needed to support programming offsets it. Another disadvantage of the antifuse technologies is that they need adjustments to the standard CMOS process.

Since antifuse technology physically alters the connections irreversibly, the approach does not lend itself to use in reconfigurable systems.

## 2.2 Electrically Erasable and Programmable Cells

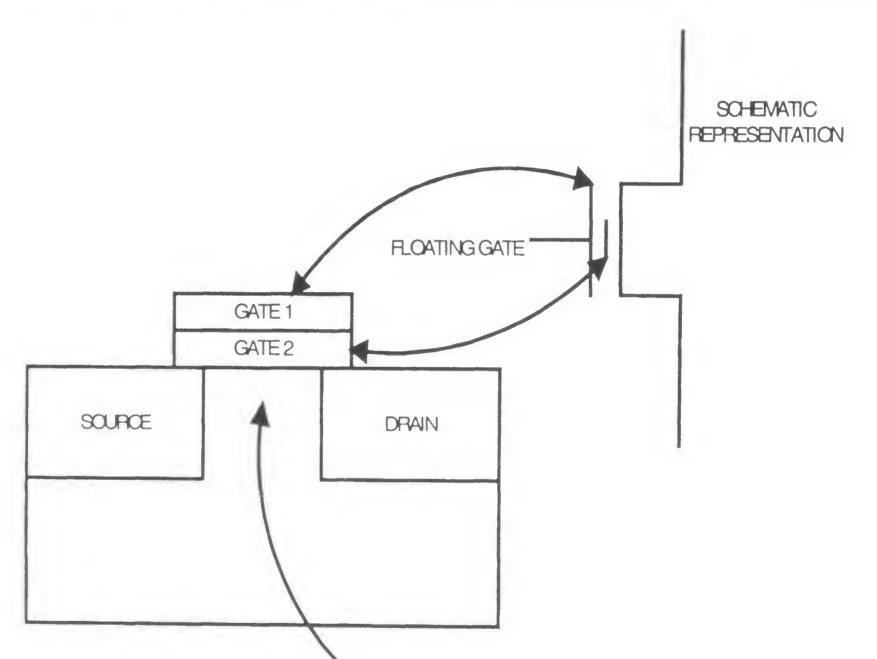

EEPROM technology was the first electrically erasable technology used for CPLDs. The programmable element is a special thin oxide capacitor that conducts a small current when enough voltage is applied across the oxide. The tunnel oxide, roughly 80 Angstroms thick, is used to inject or extract charge from a floating gate by Fowler-Nordheim (FN) tunneling. The floating gate is connected to the gate of a sense transistor in order to determine the programming state. Besides the tunnel oxide capacitor and sense transistor, two more transistors and an added control capacitor are needed to create a single EEPROM cell that can be programmed and erased.

Figure 3-2. Typical EEPROM Cell

Specifically, an EEPROM cell is a MOS transistor that stores charge on an electrically isolated, conductive capacitor plate called a floating gate. A typical cell is depicted in Figure 3-2. The floating gate is located above the transistor channel. The charge on the floating gate produces an electric field that changes the conductivity of the channel. The measure of the channel's conductivity matches the amount of the analog value stored.

A typical N-channel EEPROM cell includes an N-channel silicon-gate storage transistor. This transistor uses a floating first layer polysilicon gate (floating gate), directly accessed by a second stacked polysilicon gate (control gate), to trap and store electrons for long periods (typically decades).

The N-channel EEPROM cell is considered to be in an erased state when the floating gate has a net negative charge because of the presence of "hot electrons" injected from the drain. When the cell is in a programmed state, the electrons on the floating gate keep the N-channel transistor in a logical off state. When the floating gate is strongly programmed to a positive charge, the floating gate transistor's channel becomes conductive. This state corresponds to a binary digit, such as a logic 1.

Conversely, the cell is considered to be in a programmed state when there are no electrons on the floating gate and thus no net negative charge on the gate. To erase the cell, the energy of the electrons stored on the floating gate is raised until the electrons can "tunnel" through the tunnel dielectric from the gate to the source. When the cell is erased, the N-channel transistor is in a logical on state. Note that N-channel EEPROM cells are preferred over P-channel EEPROM cells because of the programmability and speed advantages of N-channel EEPROM cells.

If the EEPROM cell is erased, the floating gate becomes strongly negative. In this case, the EEPROM cell is nonconductive, corresponding to the complementary binary digit, a logic 0. Either programming or erasing cells in an array makes digital nonvolatile memory.

When a high voltage (typically greater than 10V) is applied over the thin insulator, electrons travel to and from the floating. This mechanism programs the cells. Erasure of the cells is affected by reversing the voltage applied during the writing process. This technique is known as hot electron injection. The high voltages needed for programming are typically produced on-chip and derived from the device supply voltage.

The tunnel oxide capacitor transports charge to and from the floating gate, which controls the sense transistor. Two extra transistors are used for the program and read operations. A control gate capacitor transfers voltage to the floating node for program and erase operations. Compared with standard CMOS logic processes, three more device structures are created for the EEPROM cell: the tunnel oxide capacitor, the control gate capacitor and the high-voltage transistor. The resulting process complexity makes the scalability of the process and the EEPROM cell more difficult in future technology generations.

## 2.3 Flash Erasable and Programmable Cells

Technically, flash technology is a variation on the EEPROM technology described above. The physics of cell programming and erasure is different from that of EEPROM cells.

Like EEPROM cells, high voltages are needed for programming and erasure. These high voltages (often greater than 10V) are typically produced on-chip and drawn from the supply voltage.

The flash EEPROM cell typically incorporates its floating gate into the device structure for improved cell area. By adding an NMOS transistor in series, the flash transistor can be incorporated into the basic cell.

The behavior of an individual flash transistor is changed with a program or an erase operation. When a flash transistor is in the erased state, the threshold voltage (that is, the voltage at which the device turns on) is about 1 V. During programming, the threshold voltage increases above 5.5 V, so the transistor does not turn on for a logic operation.

The physical implementation of the flash transistor includes a floating gate polysilicon layer that is isolated from the silicon substrate by a thin oxide layer roughly 100 angstroms thick. Above the floating gate is the control gate polysilicon layer, with an insulating oxide-nitride-oxide layer between them. The control gate is driven by internal logic circuits while the floating gate is unconnected. When the flash transistor is in the erased state, there is no net charge on the floating gate. By changing the electrical charge on the floating gate, the threshold voltage may be increased.

The structure of the flash memory cell and EEPROM memory cell is therefore similar.

During the programming operation, channel hot electrons (CHE) are created near the pinch-off region. Some CHEs have enough thermal energy to pass through the thin oxide and remain on the floating gate. The collected electrons create a net negative voltage on the floating gate that opposes the electric field emanating from the control gate. The result is a net increase in the threshold voltage.

Applying 0 volts to the control gate and around 10 volts to the source erases the flash transistor with the drain left floating. The electric field between the floating gate and the source node is increased to the point where Fowler-Nordheim tunneling takes place. Excess electrons are transported from the floating gate to the source. The transistor is designed to make the erase process self-limiting. The electric field decreases as electrons are removed from the floating gate. FN tunneling effectively stops when the floating gate is electrically neutral.

Once the basic memory cell is in place, additional control logic must surround it to allow addressable reading and writing. The fully controlled and programmable flash cell is typically one transistor smaller than the equivalent EEPROM cell. That results in a simpler cell structure, smaller cell size and potentially higher integration density.

Flash EEPROMs typically use Fowler-Nordheim tunneling, as opposed to hot-electron injection, for cell programming as well as for cell erase. A voltage signal, usually less than 25 volts, is applied to the control gate. The control gate is capacitively coupled to the floating gate. The drain is held either at ground potential or at a voltage less than that applied to the control gate, and the source is held at ground potential. Under such conditions, Fowler-Nordheim tunneling occurs, in which electrons from the drain, tunnel through a thin layer of SiO2 (tunnel dielectric) to the floating gate.

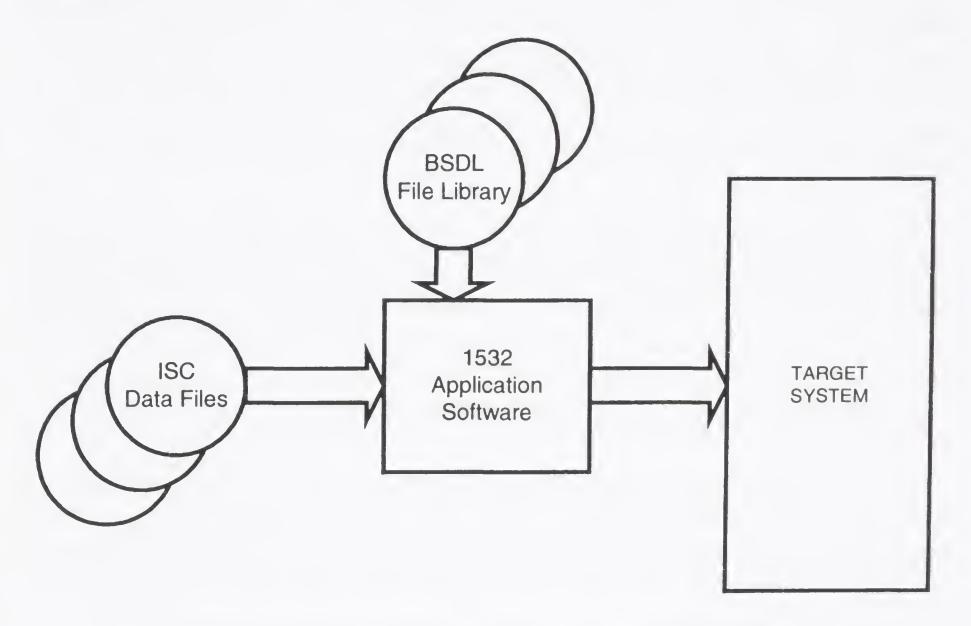

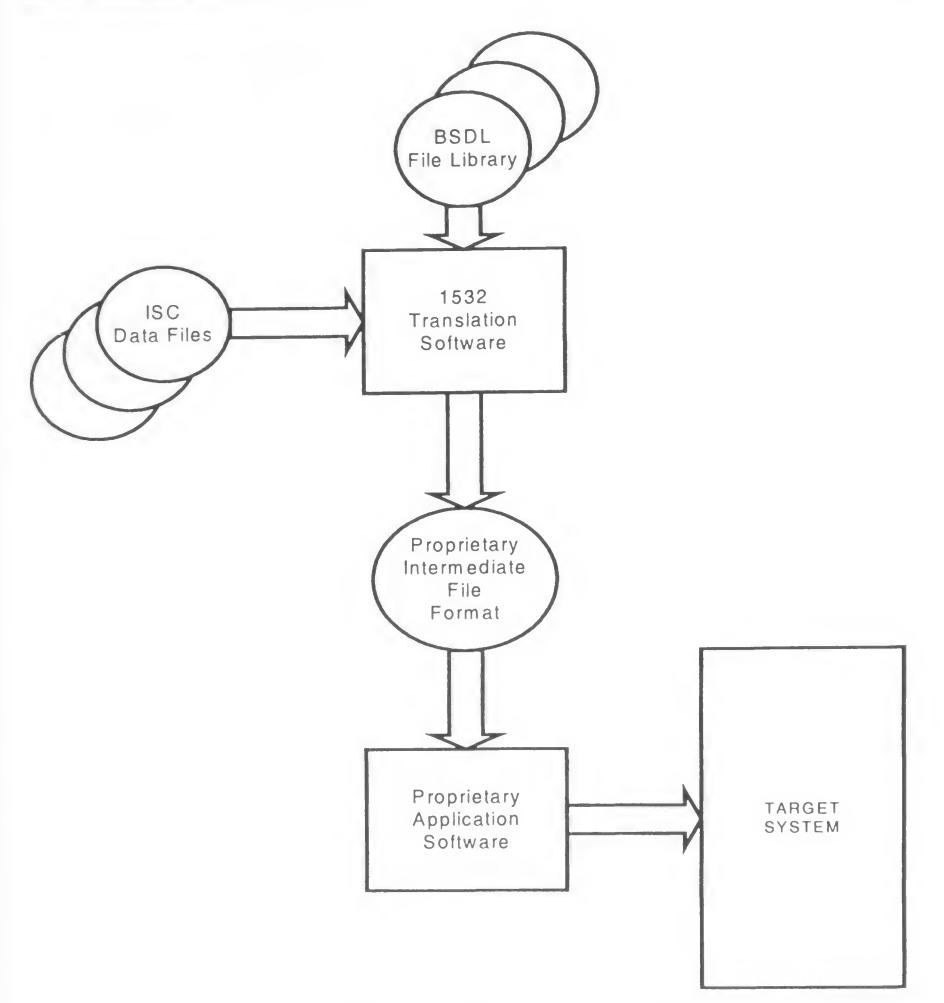

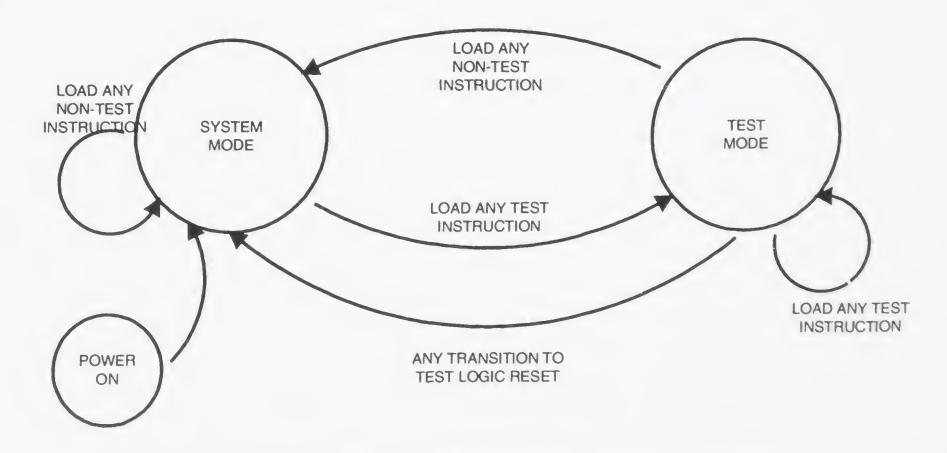

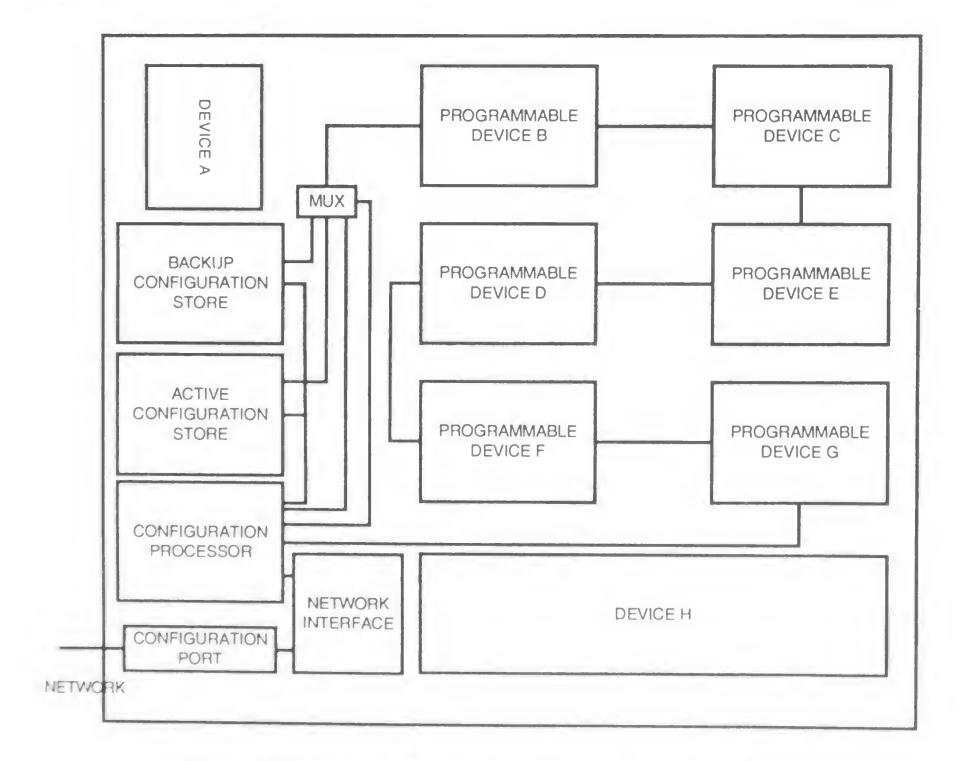

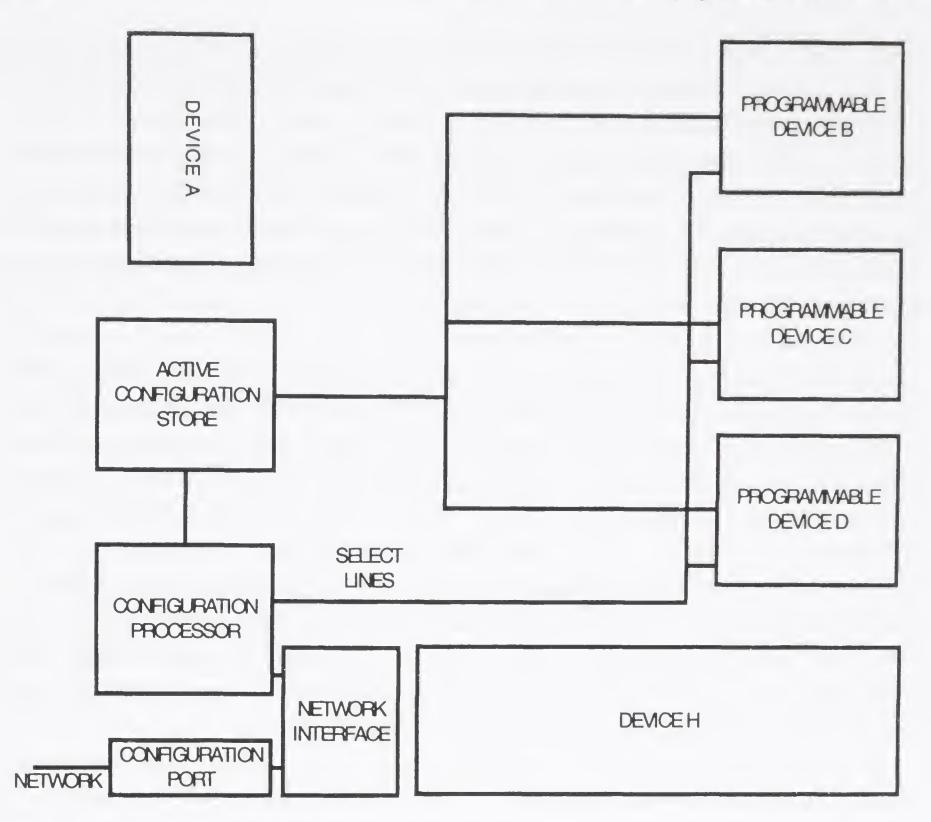

A conventional EEPROM cell electrically induces Fowler-Nordheim electron tunneling to erase the floating polysilicon gate. A high voltage signal (typically greater than 10V) is applied to the cell drain while the control gate is held at ground potential and the source is left at a floating, or unspecified, voltage potential. As a result, the electrons stored on the floating gate will tunnel through the tunnel dielectric to the source.